Tool/software: WEBENCH® Design Tools

Hi,

I have used Webbench power designer to design a 5V regulator using the TPS53318 part. Schematic is attached.

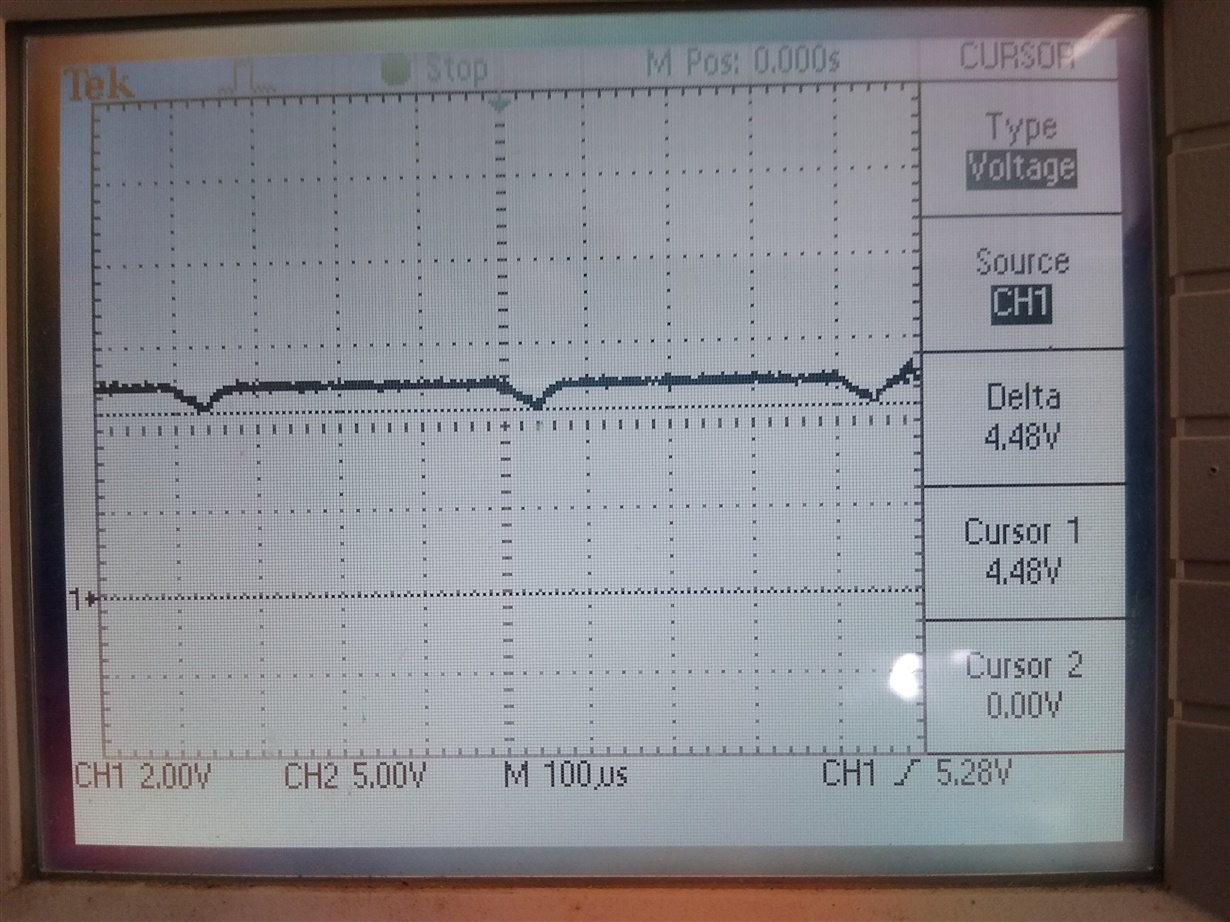

I have looked at all of the voltages on the board an all look correct, but the device doesn't switch - there is very low - no output (0.07V)

DC Voltages measured at nets names on attached schematic:

VIN: 12.0VDC

EN: 1.3V

TRIP: 0.4V

MODE: 0.12V

PGOOD: 0V

VREG: 5.0V

VBOOST: 5.0V

L1: 0.07V

VOUT: 0.07V

VFB: 0.014

What am I doing wrong? Thanks!