Other Parts Discussed in Thread: TPS2115A, LM66100

Hi, team

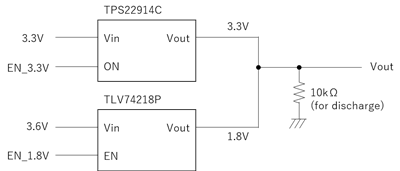

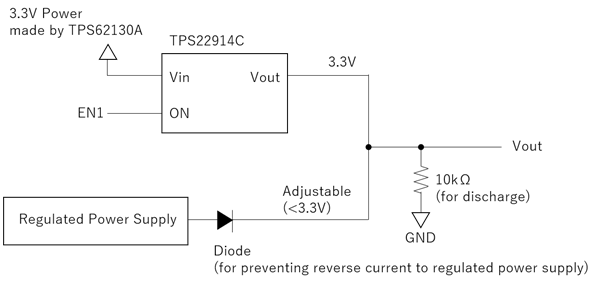

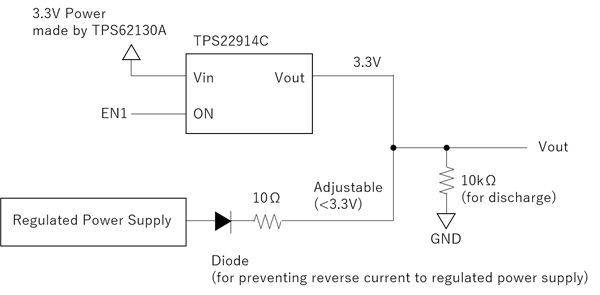

I designed Power MUX using TPS22914C and TLV74218P as below.

In measurement, delay time was 1.8ms when rising 1.8 to 3.3V.

In datasheet of TPS22914C, delay time is 913us (typ).

In the case external voltage applied, is there the factor delay time extend?

Best regards,

Naoki