Hello team,

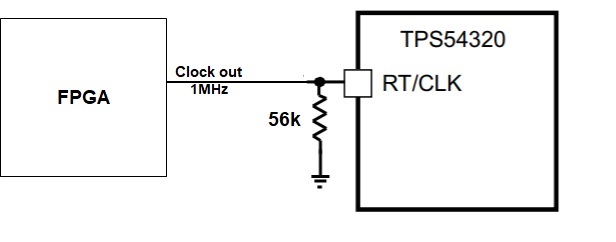

I am considering how to use TPS54320 1MHz external clock to decide switching frequency. I designed below block diagram.

During power on, I set IO of FPGA IO as Hi-Z and TPS54320 power on by internal clock set by RT(56k). But the leak current from FPGA is too large during Hi-Z, and the current in RT/CLK pin changed from the desired current value, the switching frequency was increased. So I am considering how I should configure RT/CLK pin.

Would you please advise me to avoid increase switching frequency and best configuration between RT/CLK pin and FPGA output?

Your support would be so appreciated.

Best Regards,

Akihisa Tamazaki