Hi, There

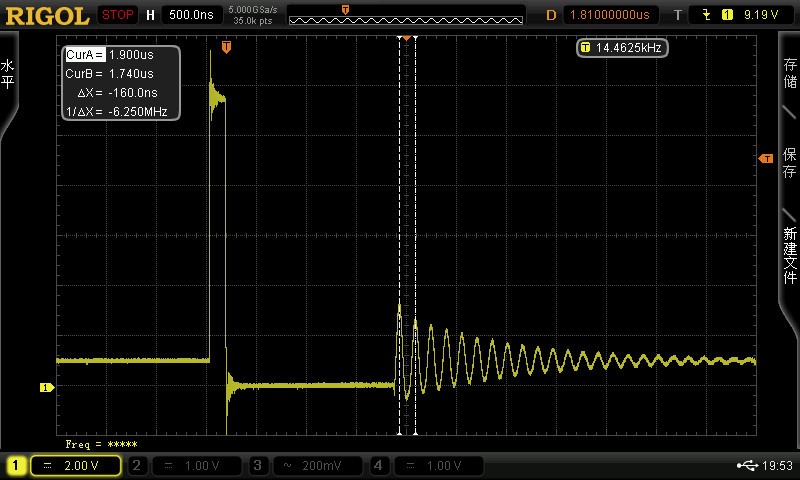

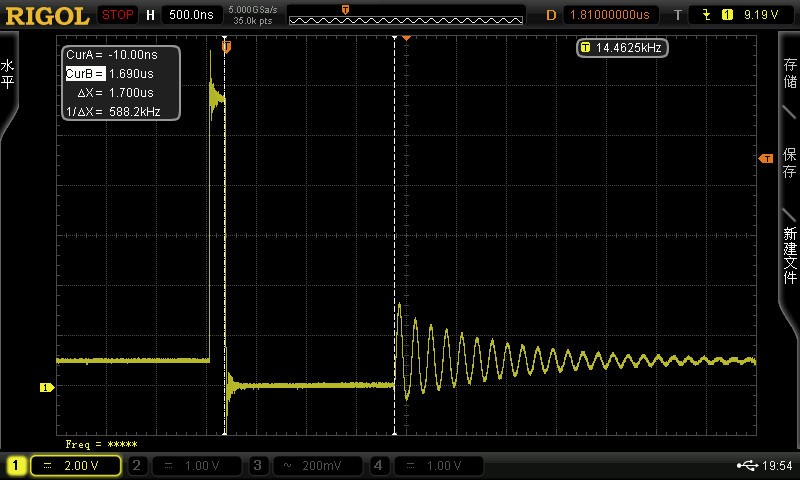

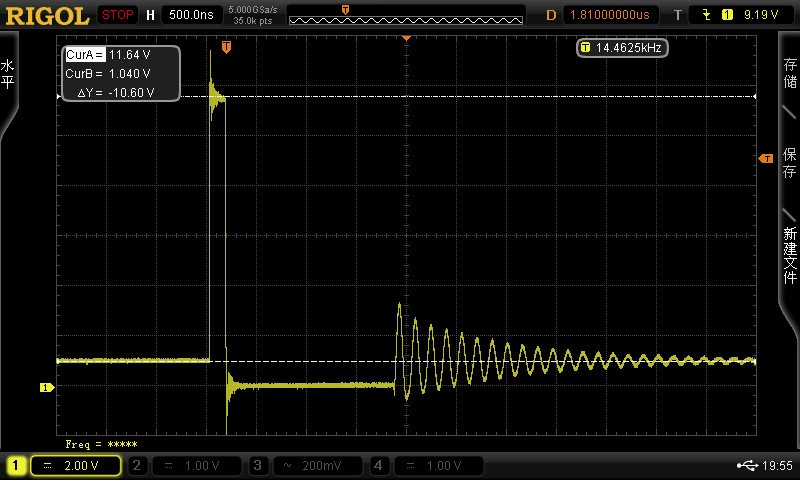

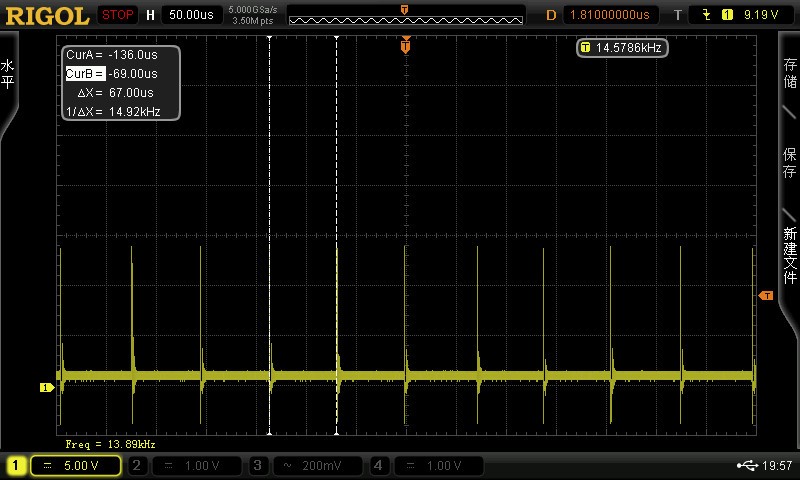

We are using TPS54394 as our power solution:

1.CH1 is 3.3V@1.5A,and Cout is around 100uF;

2 CH2 is 1.0V@2A, and Cout=660uF according to FPGA requirment.

3. Vin=12V ,Vinmax=14V

Per TPS54394's spec, Cout range is 22-68uF.

And we found FPGA & 3.3V suppplied chip damged(shorted) during power up, failure rate some times can reach to 10%.

It is related with out Cout cappacitor selection?

Any suggestion how to debug it?