Other Parts Discussed in Thread: DAC53608

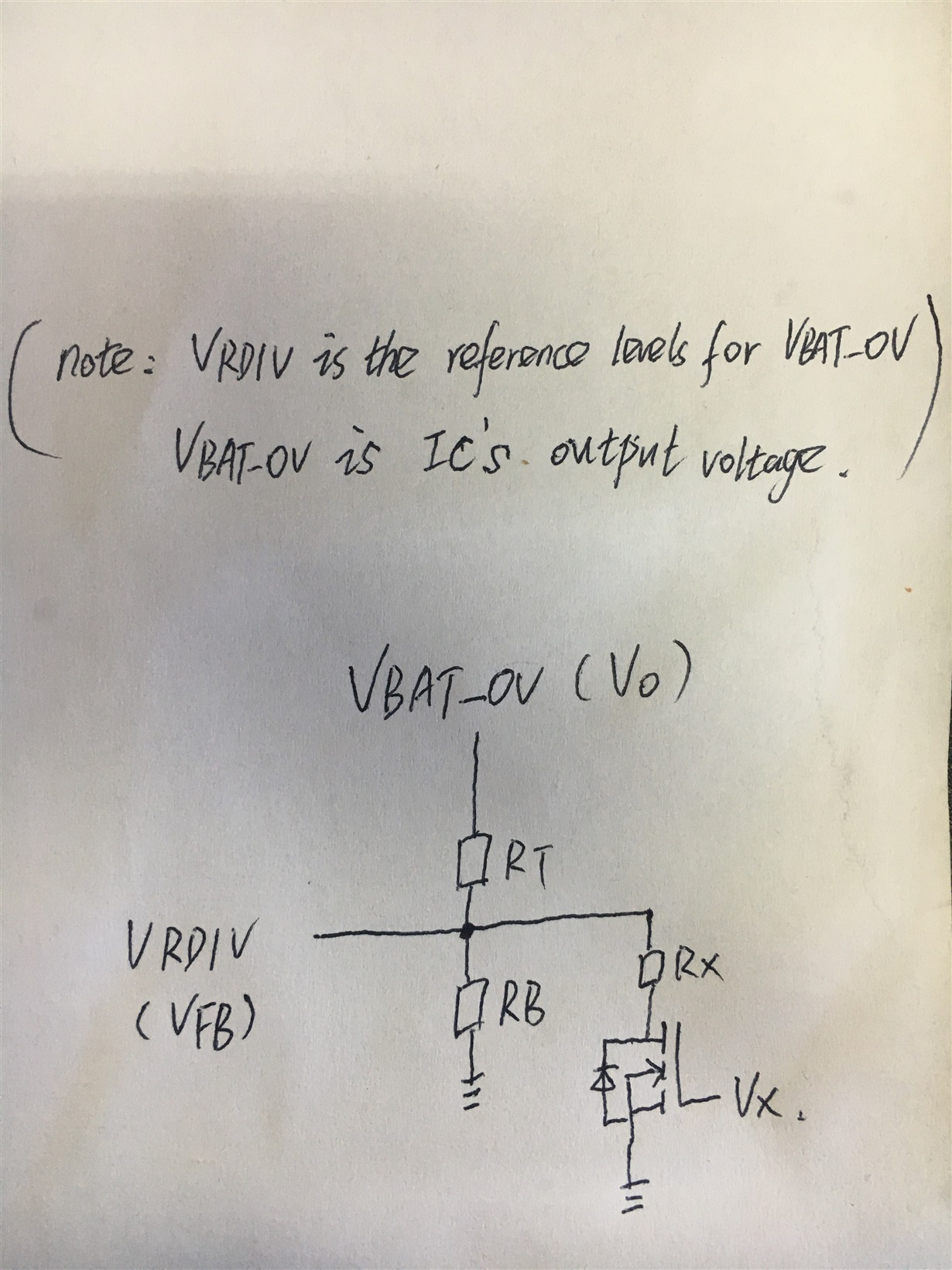

The output range of the front-stage power management chip is 2.2-5.5V, and the adjustable range is around 1V. How to make the output voltage dynamically adjust? With analog power chips? How do You choose an architecture? Please recommend

Regards,

Regards,