I created a deign for the TPS54A24 on webench and put all the capacitors in the design, however my input and output are both still very noisy especially during loading. What are the possible solutions besides just gluing on more capacitors.

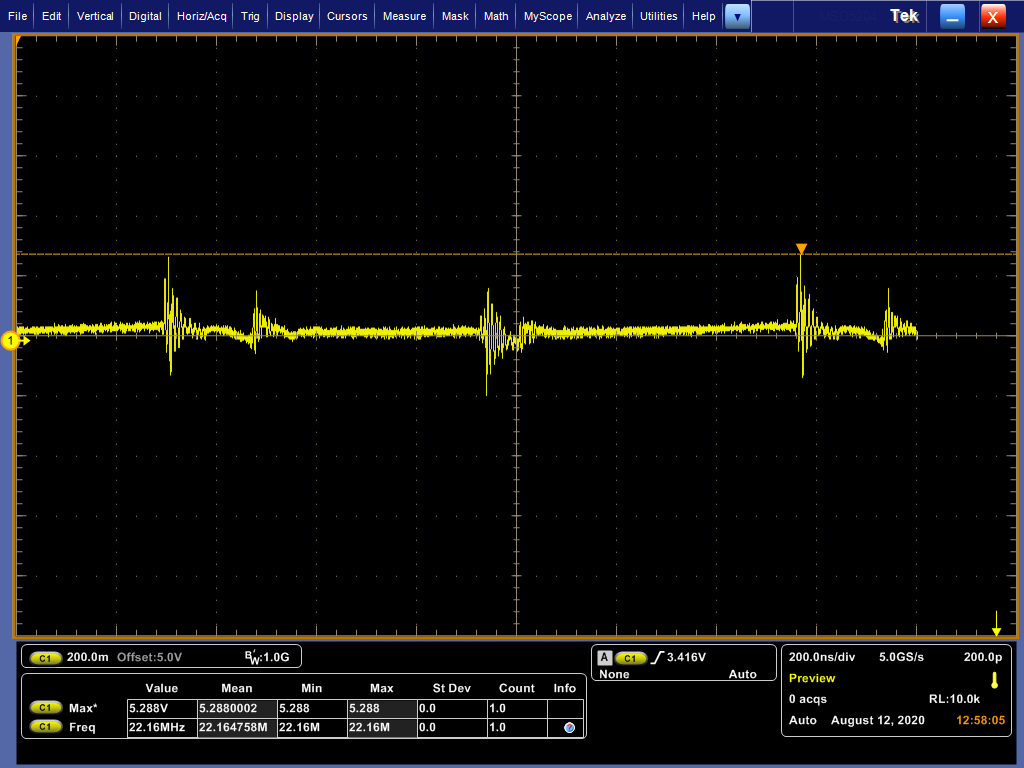

This first image is the 5V input rail during no load

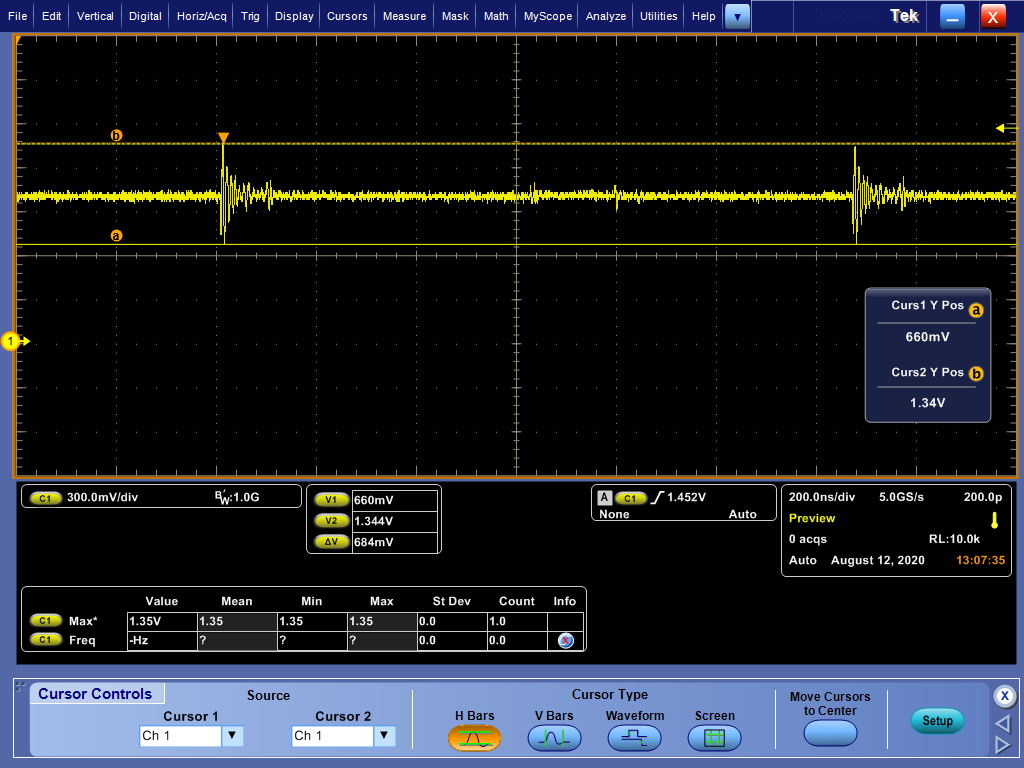

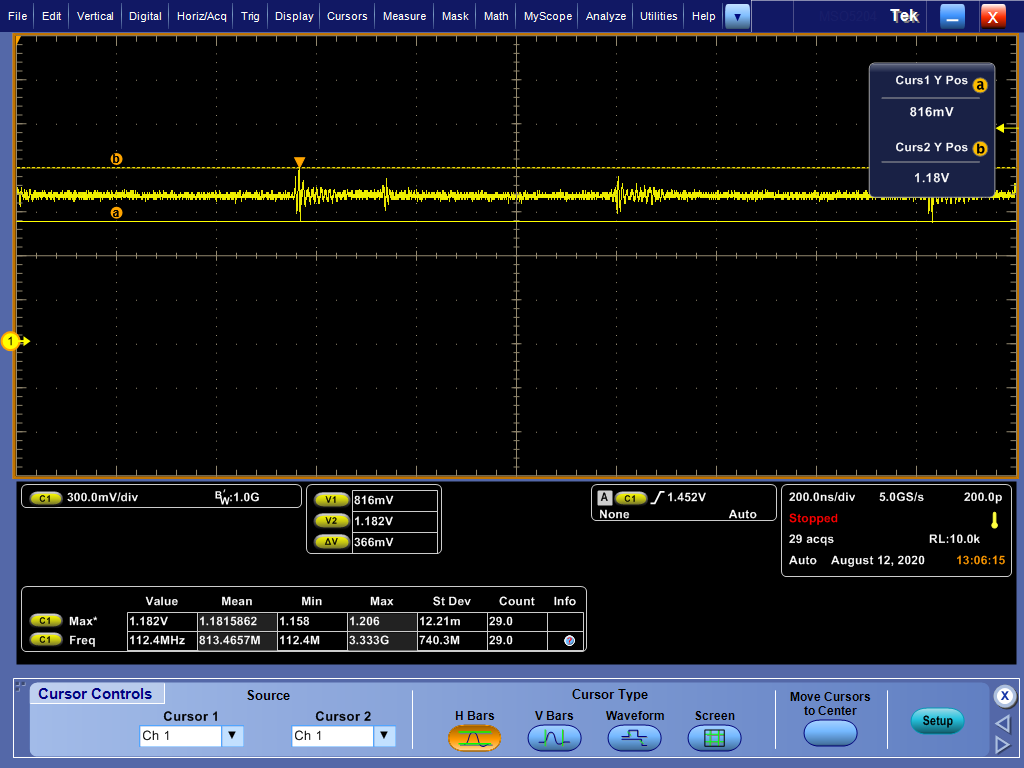

The second image is the 1v output rail in no load

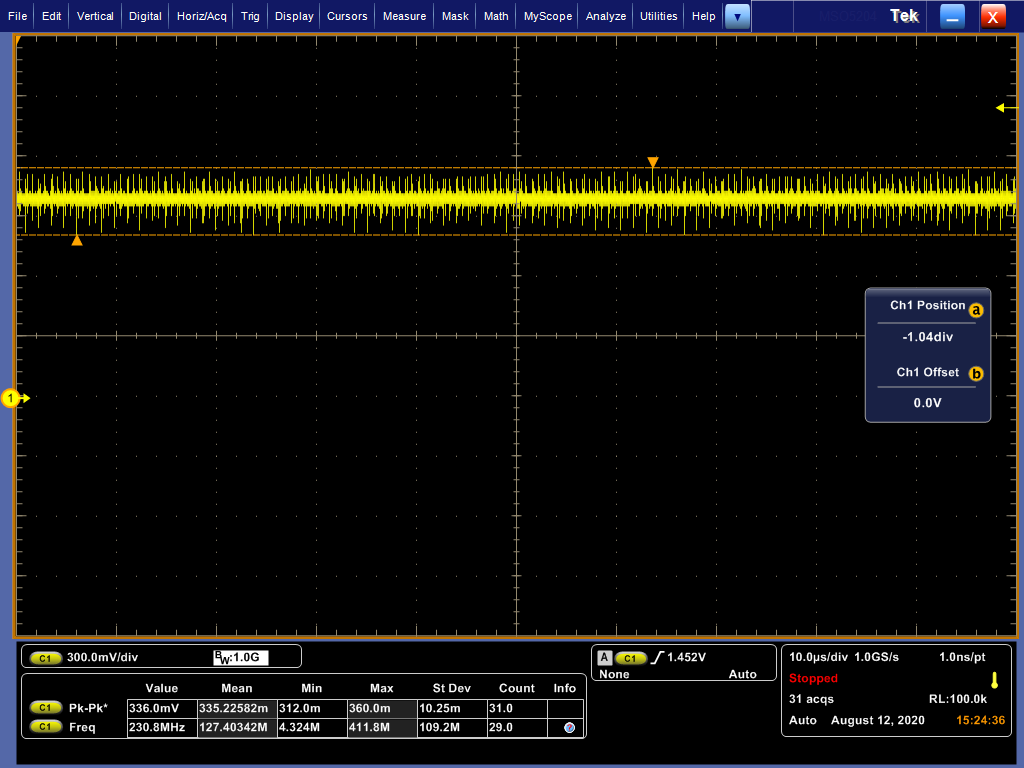

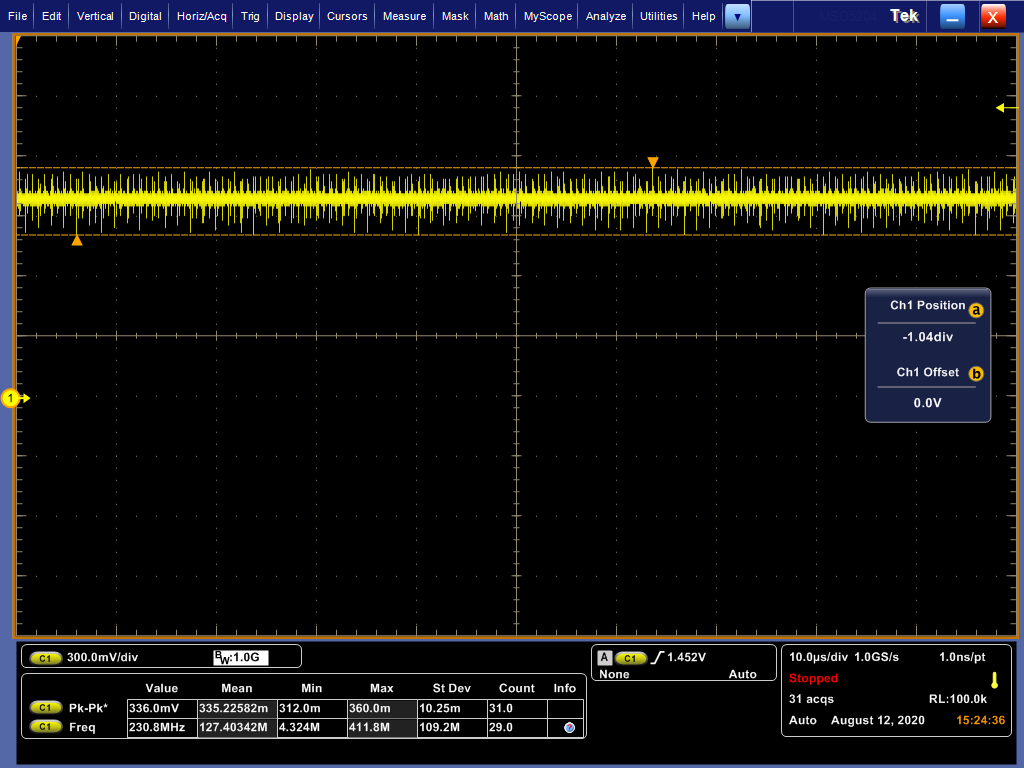

The third image is the 1v rail during a 0.6A load

This is the webench schematic I used.