Hello,

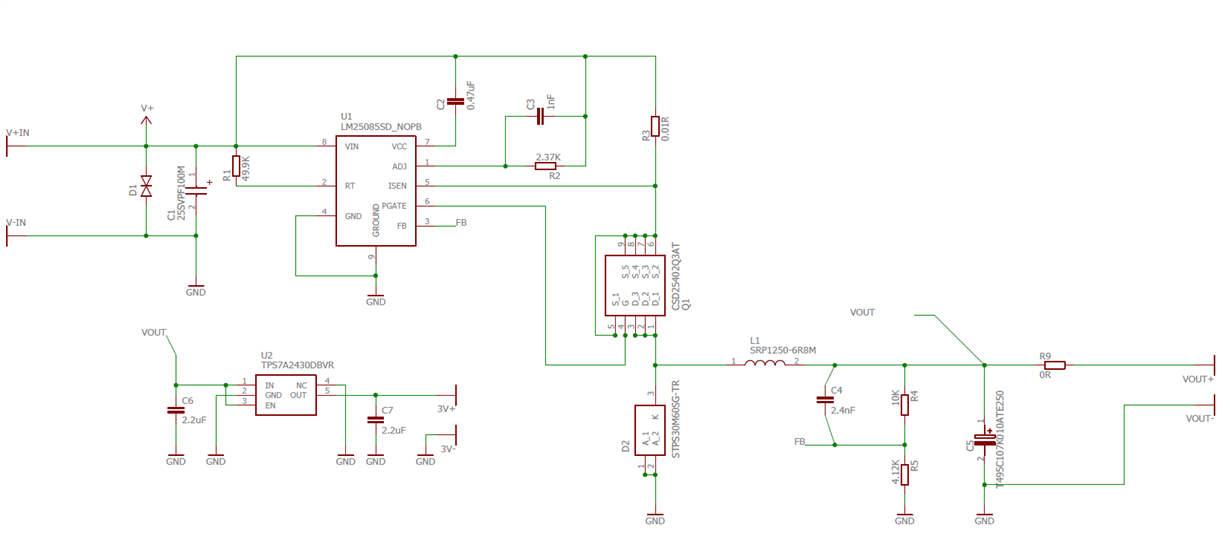

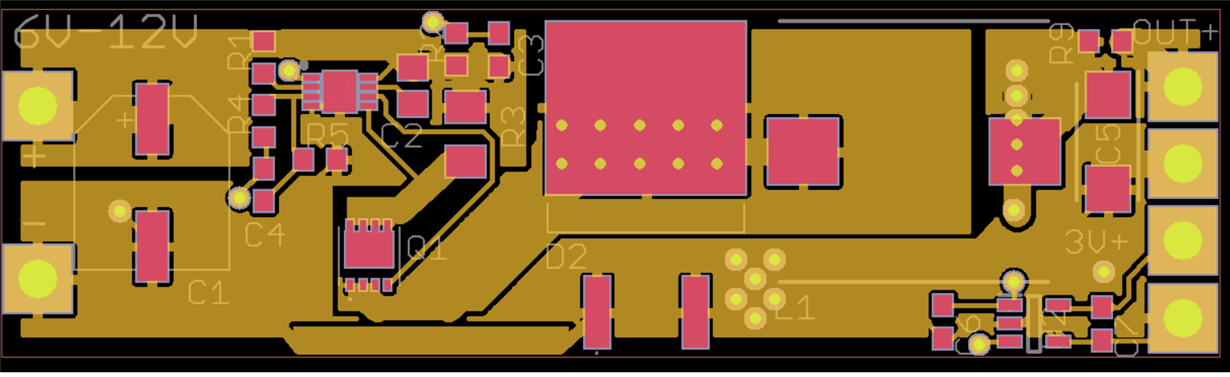

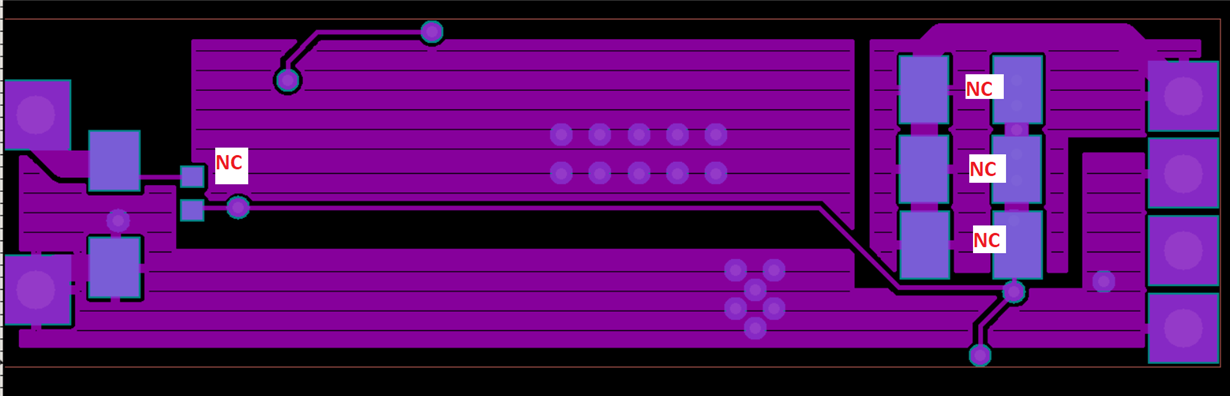

I used WEBENCH to design a regulator (VinMin = 4.5V VinMax = 16.0V Vout = 4.3V Iout = 5.5A), the main regulator is a LM25085 ( I use also a second LDO to generate a 2.5V for other purpose) , circuit is attached and also the WEBENCH report.

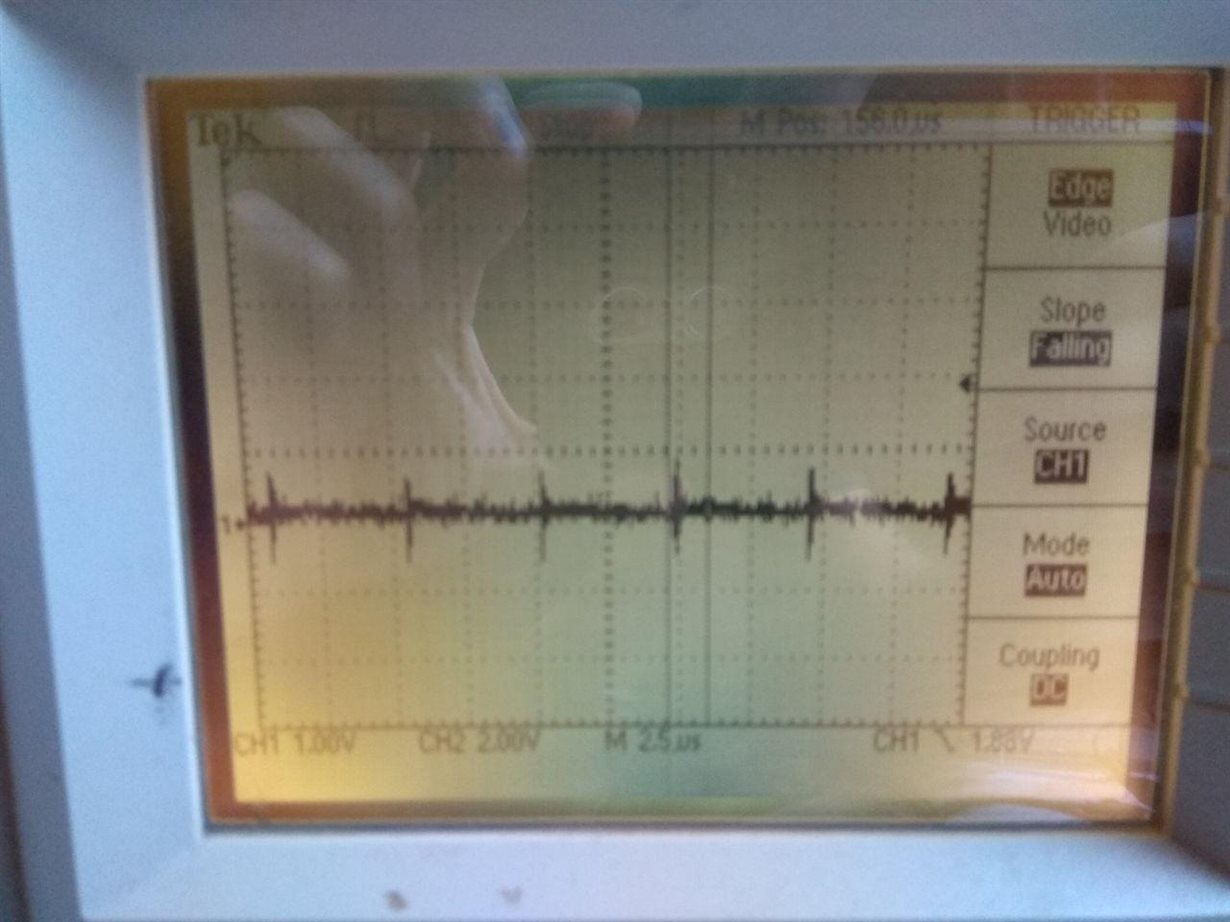

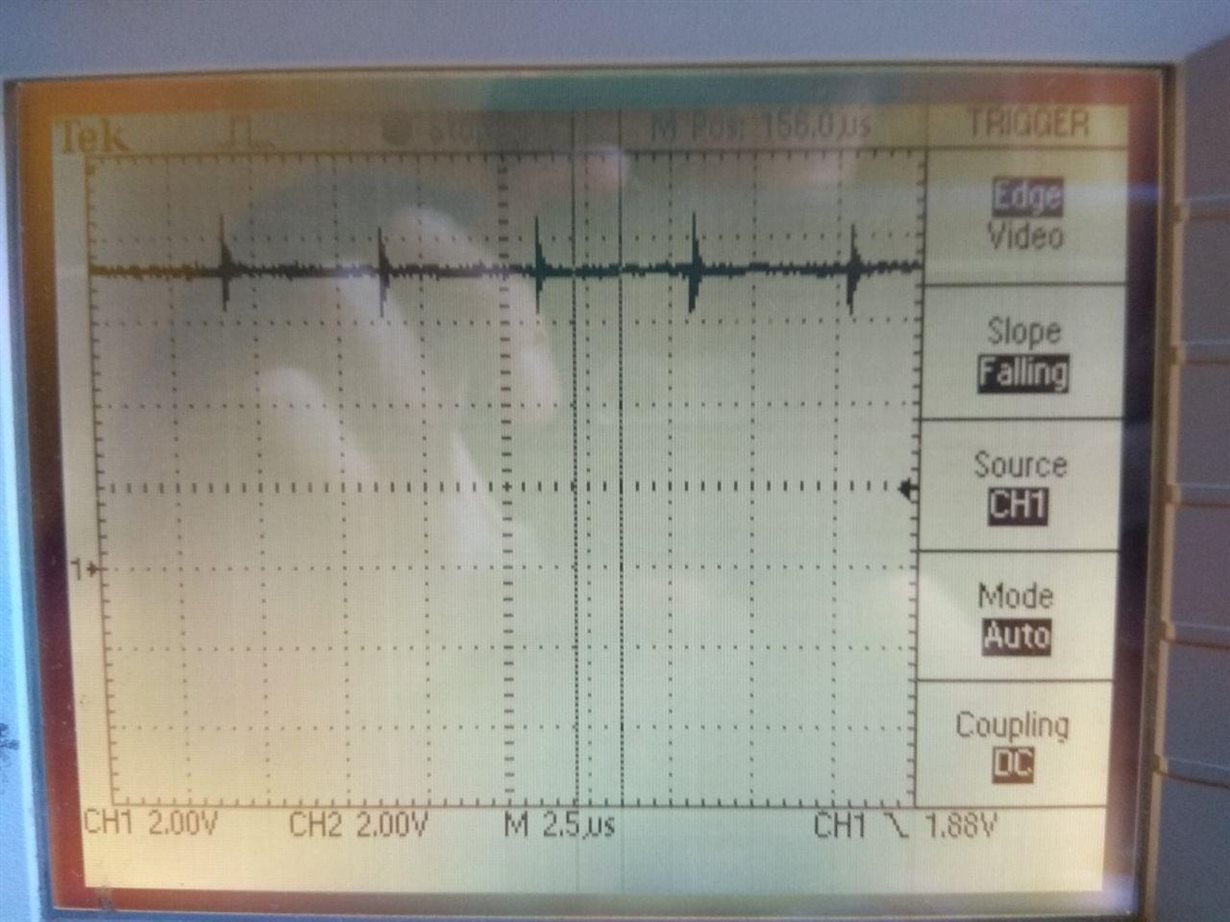

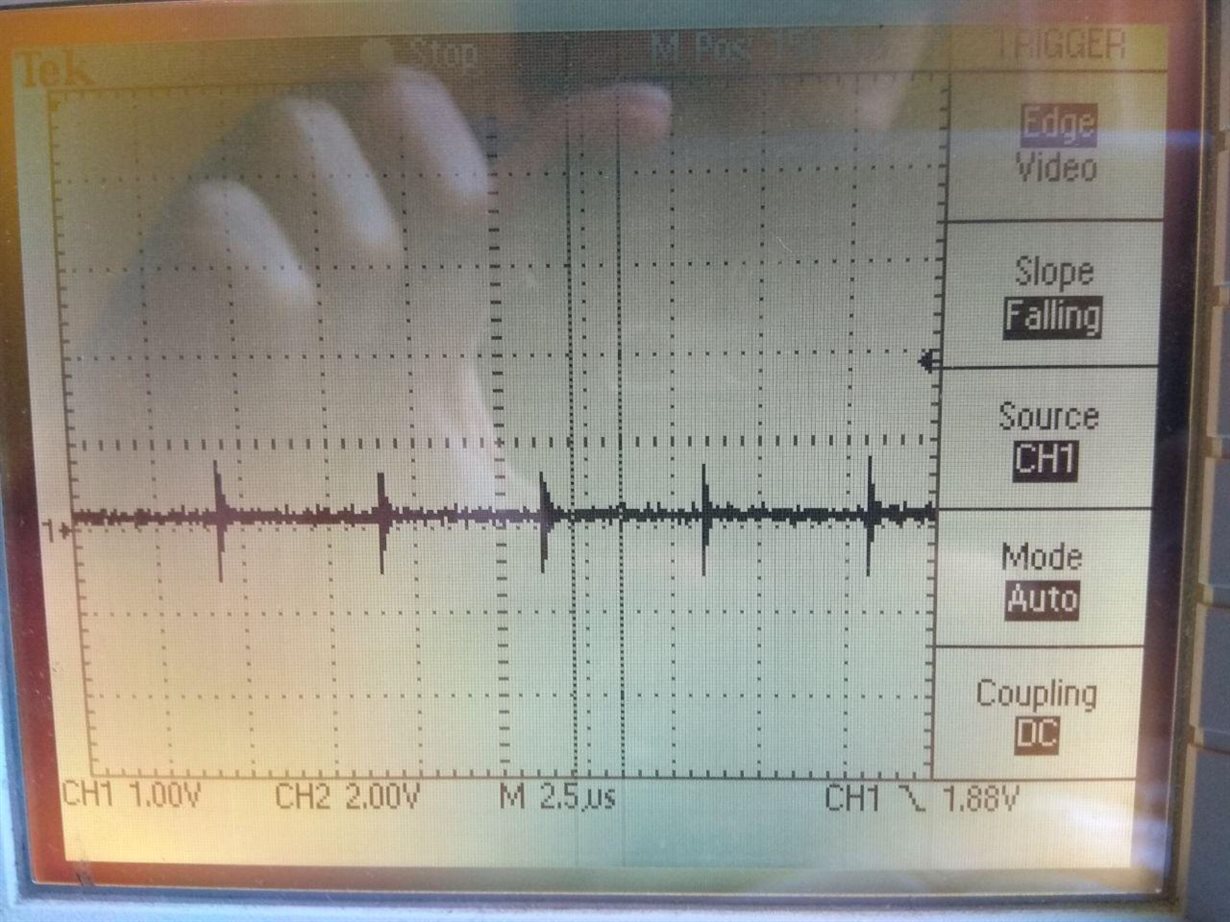

I have just get the PCB and the output is correct when there is no load (Vout = 4.3V).

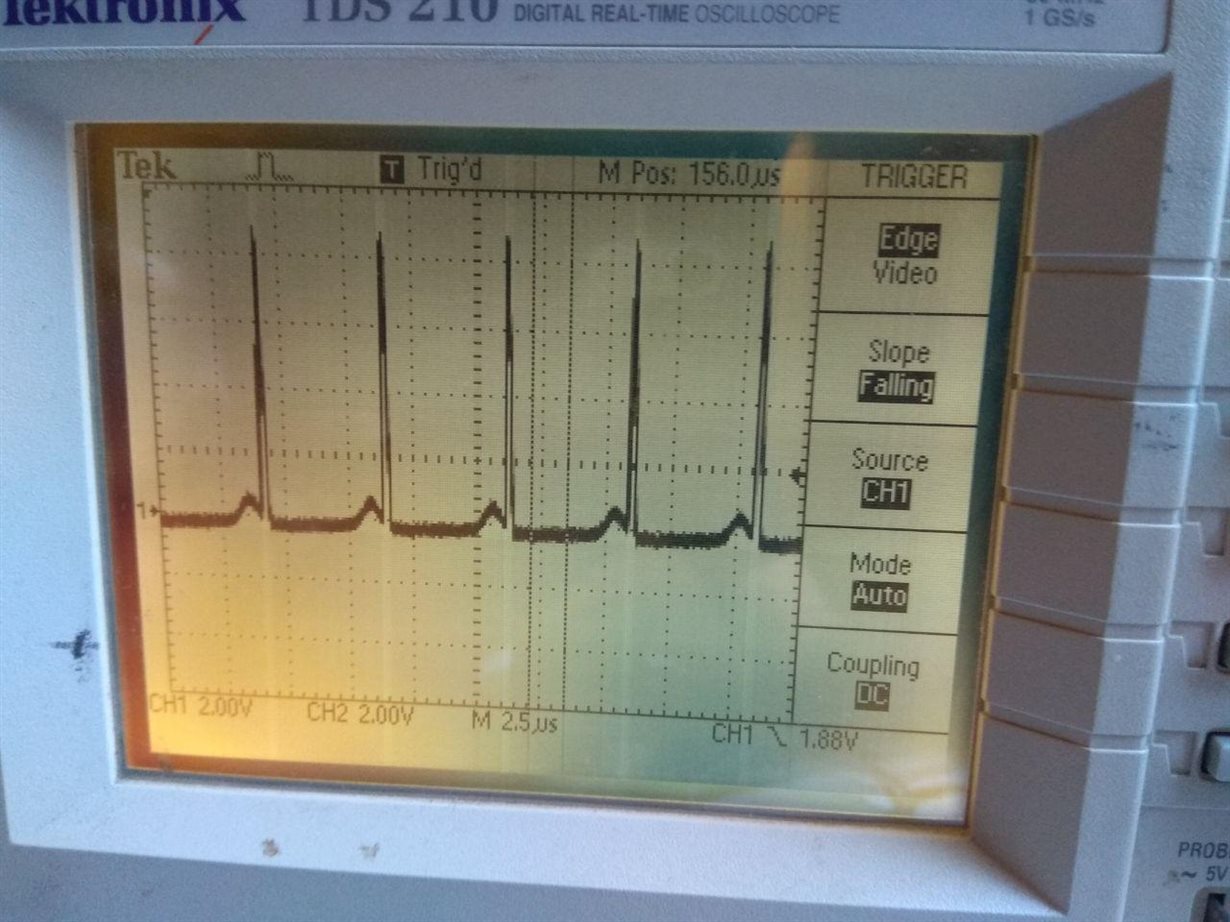

When a load is connected (1 Ohm resistor) the current seems to be limited to 0.01A at Vin = 7V, and it drop to 0.002A at Vin = 11V.

I checked the components values and they seems OK. I have no idea how to debug the problem, any mistake on the circuit ? Any advice ?

Best regards,

RiccardoWBDesign22.pdf