Hello

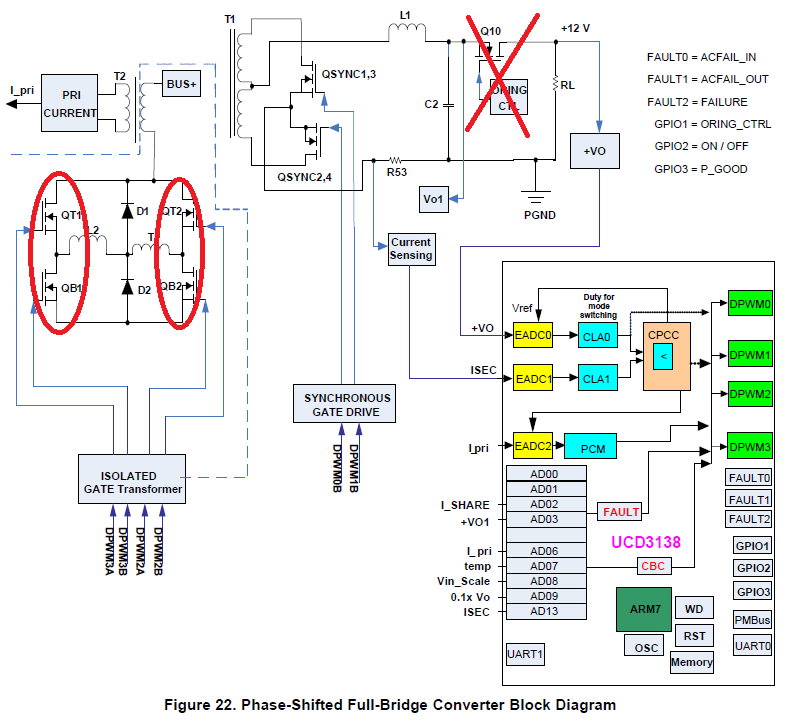

I recently tested UCD3138-PSFB EVM and found two problems:

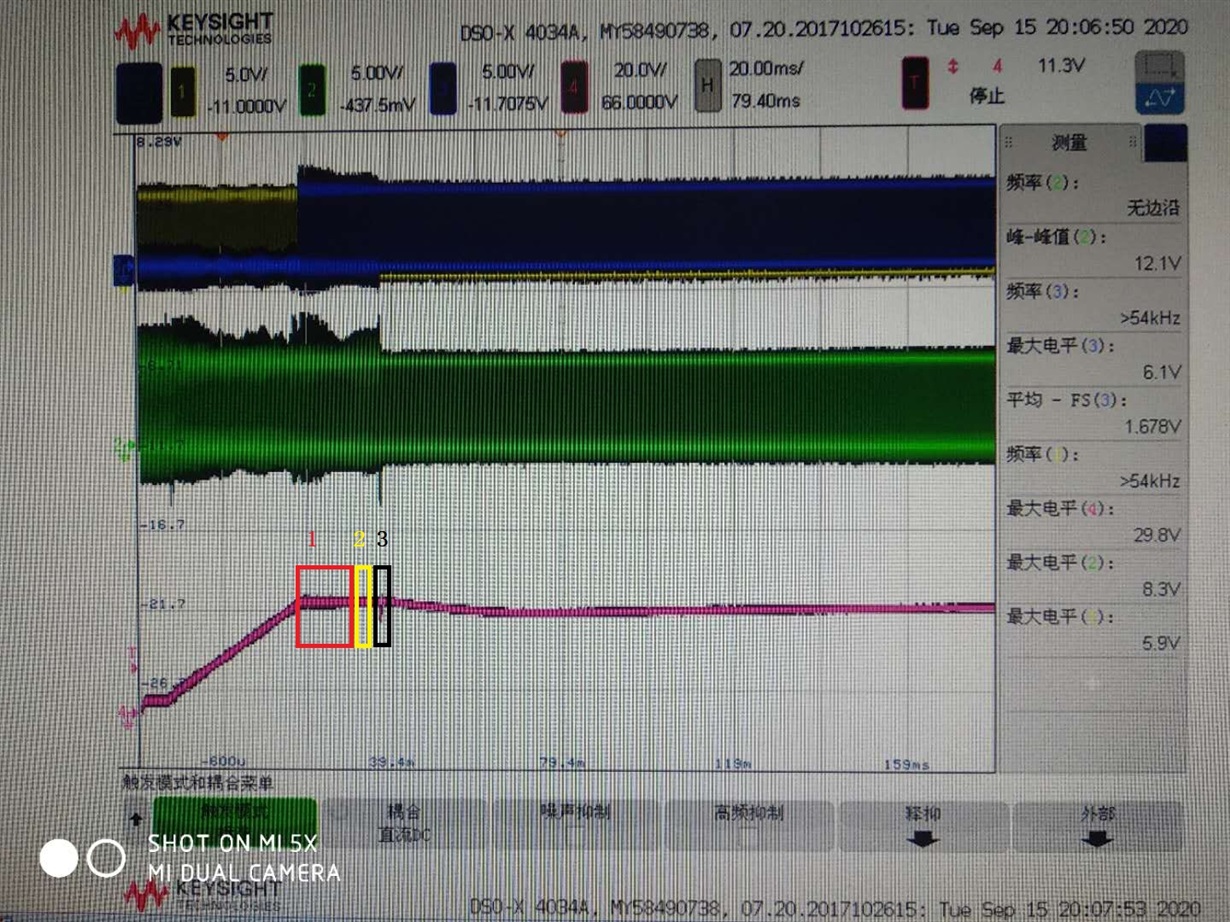

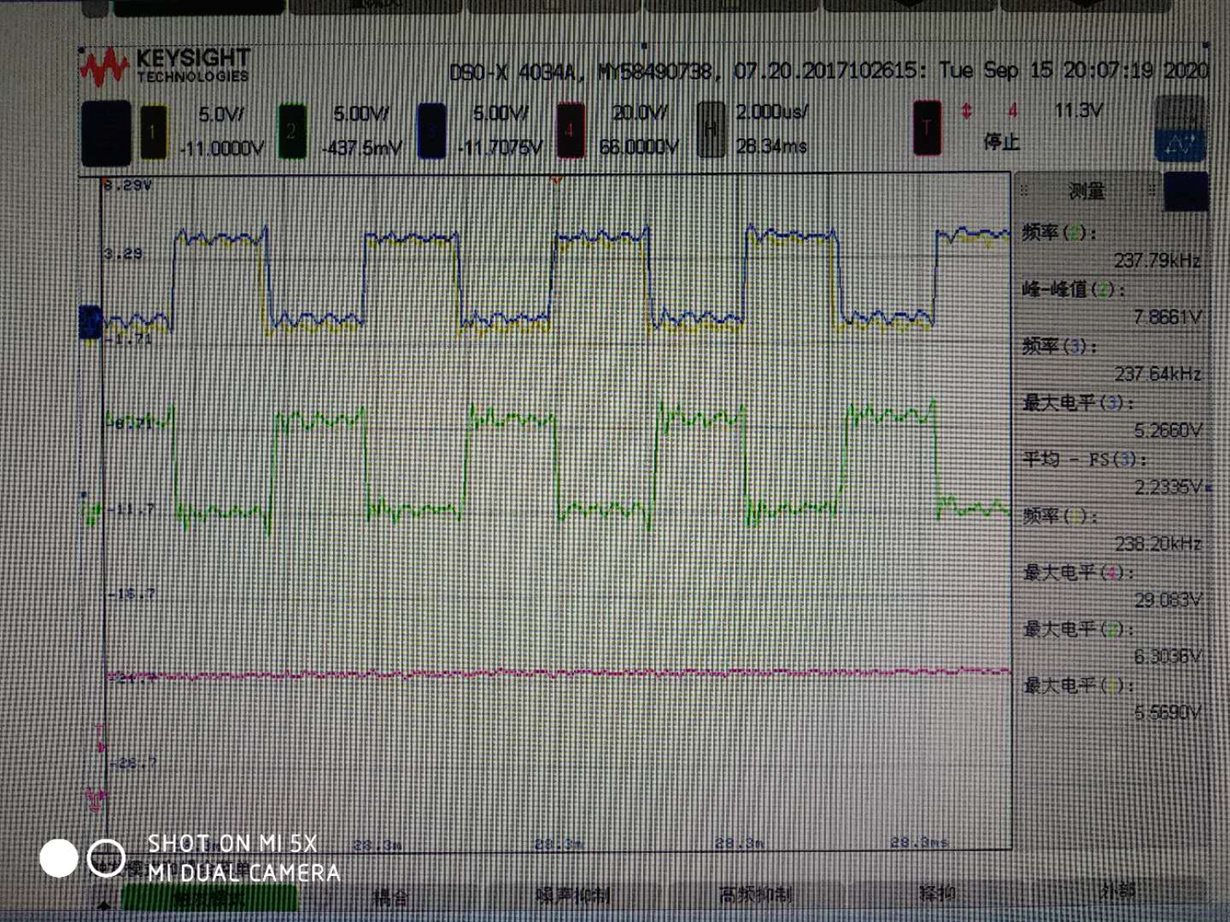

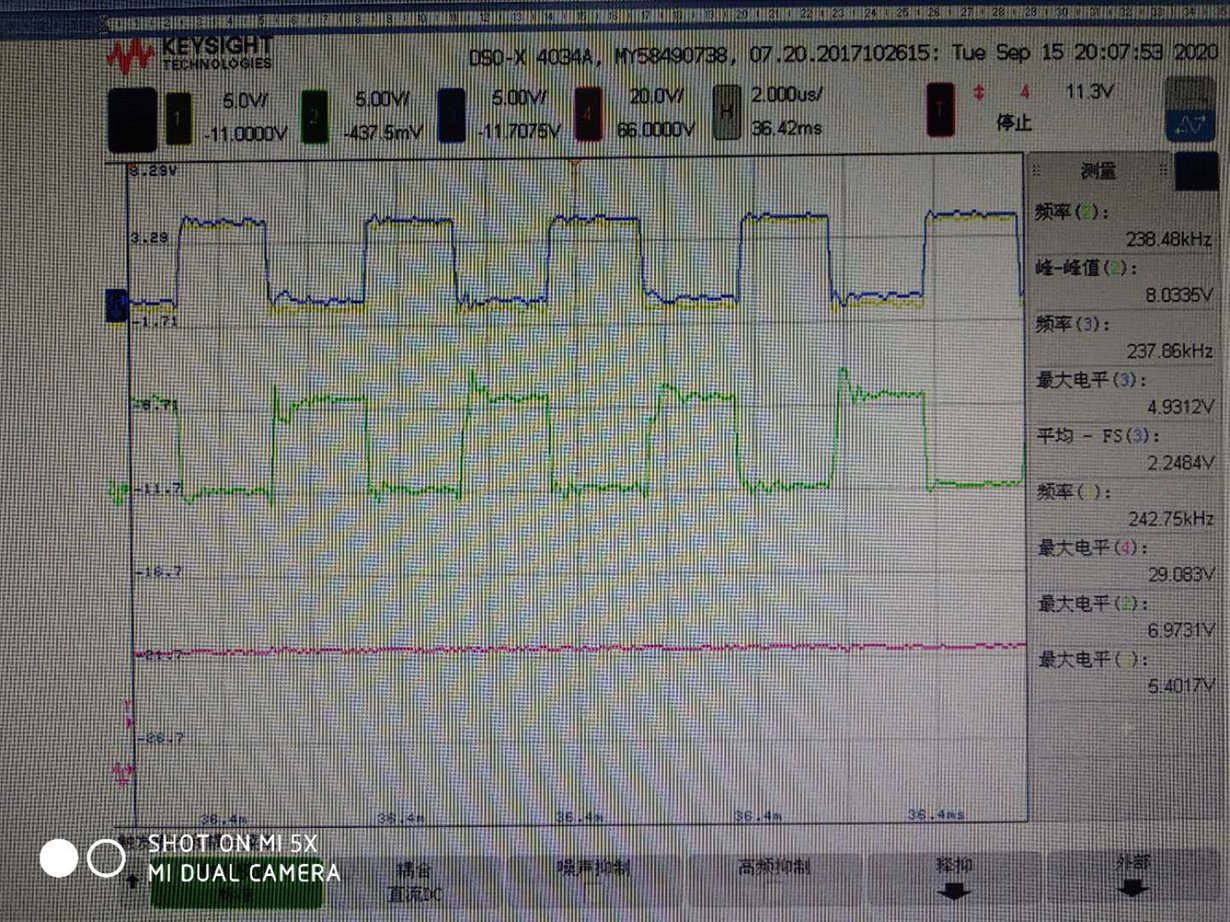

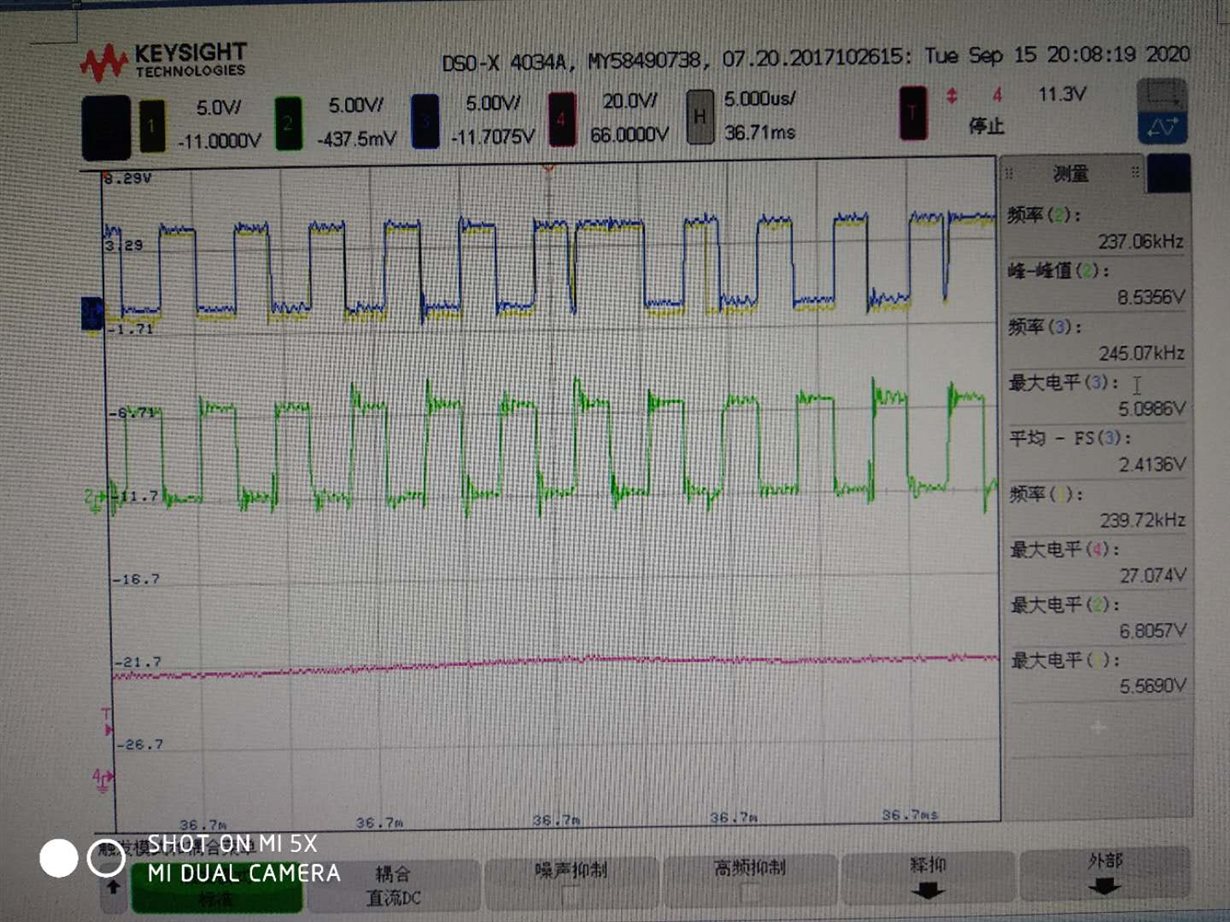

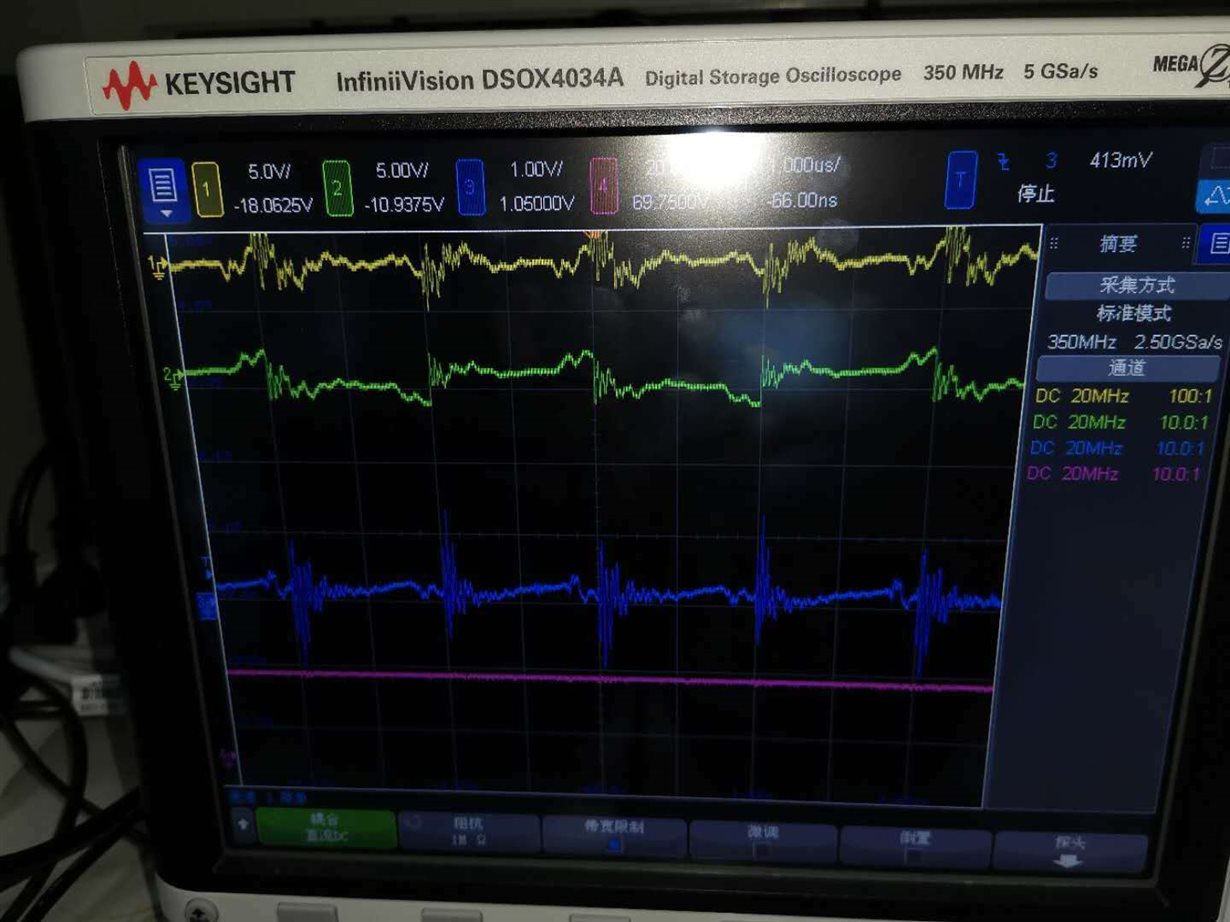

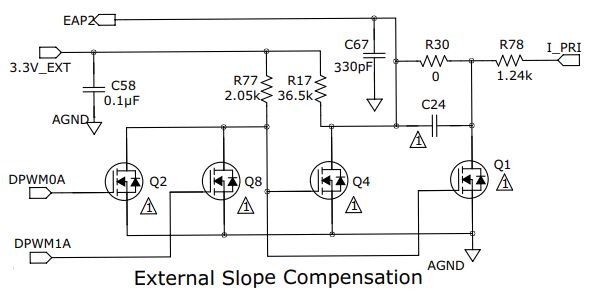

1. When the development board is unloaded and slightly loaded, the phase shift angle of the primary switch tube is very different. When there is no load, the phase shift angle is large. At light load and full load, the phase shift angle is small and the difference is not big.

why is it like this?

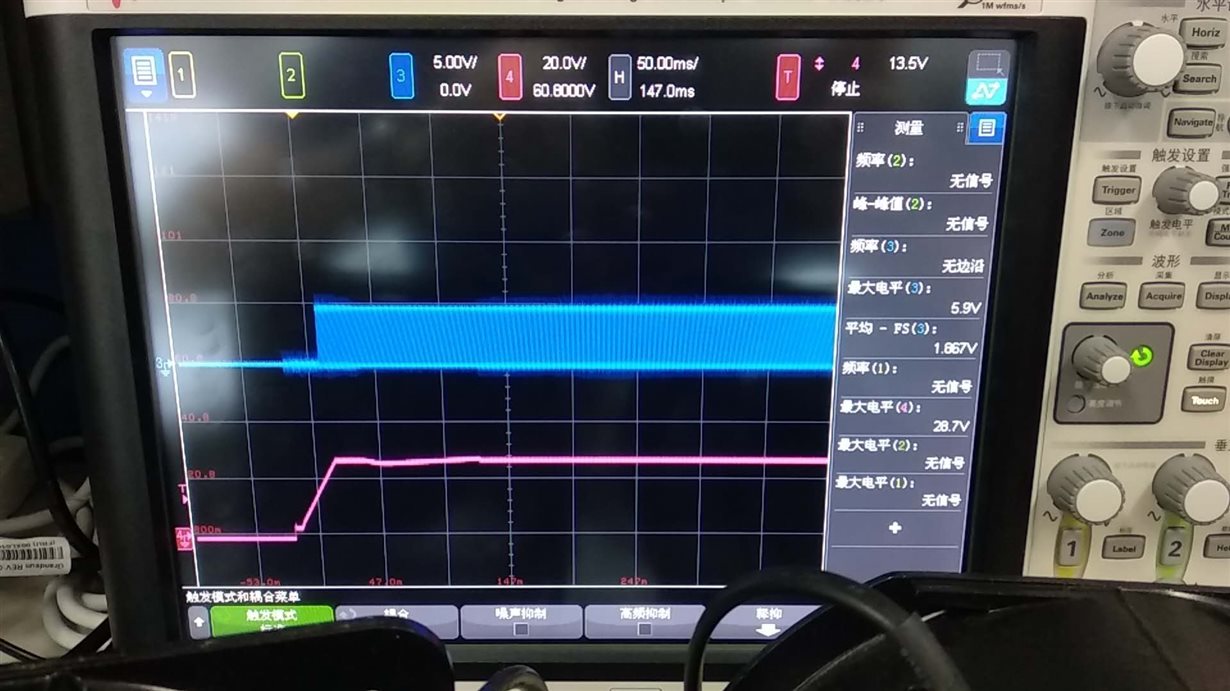

2. If the dead load on the development board is removed, the output voltage will drift up.

Why must add 20mA dead load?