Other Parts Discussed in Thread: TPS53679,

Hello,

Our design is TPS53679+ CSD95490Q5MC (4+1) for Intel D-2100.

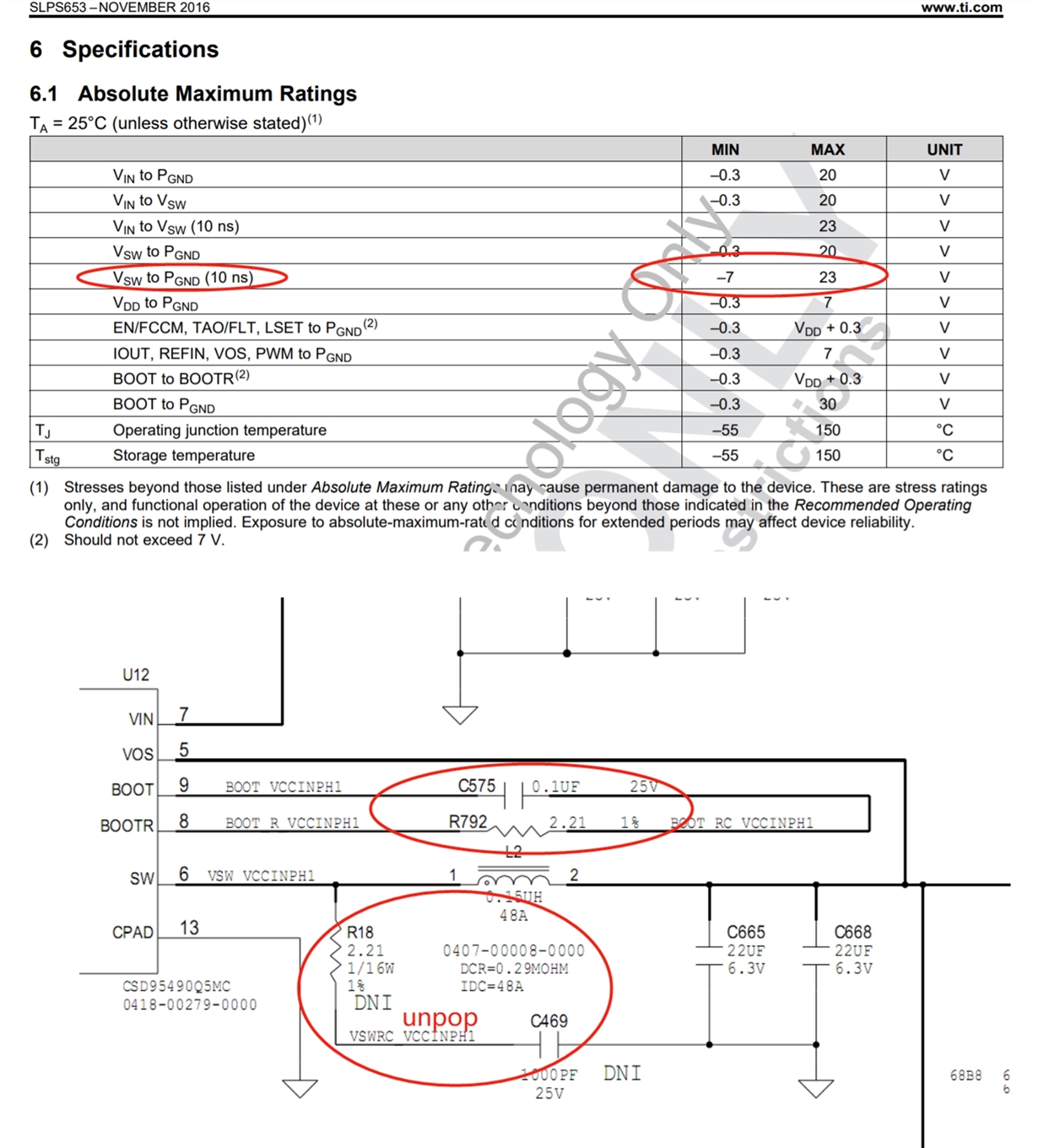

In CSD95490Q5MC datasheet Absolute Maximum Ratings has '' Vsw to Pgnd (10ns) ,min=-7v,max=23v".

Our design observes CSD95490Q5MC's Vsw is min=-5v,max=19v, BUT -5v is about 17ns.