Hi there,

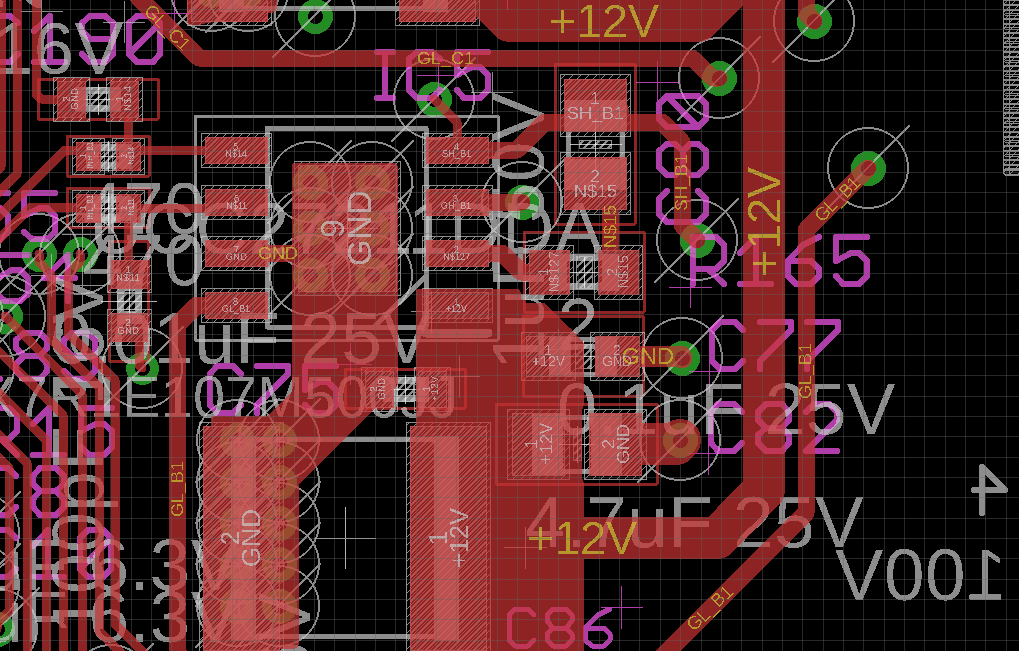

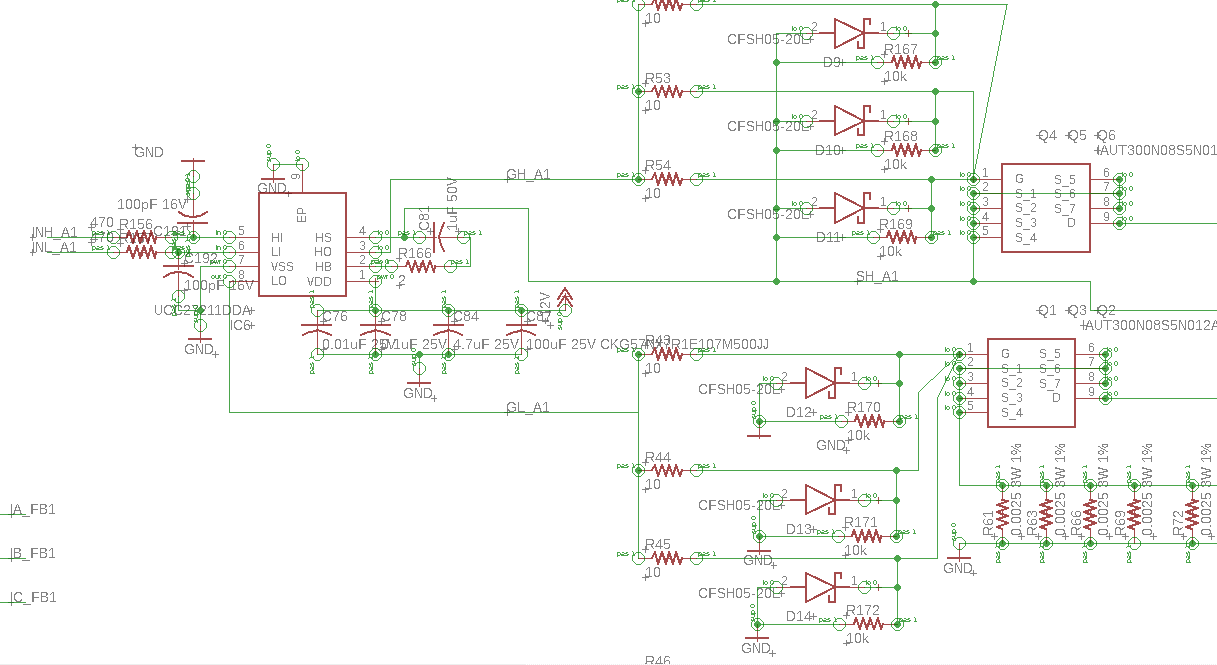

I have designed a 50V 5KW motor controller board with the UCC27211 where I am switching 3 mosfets in parallel. Each of the 3 UCC27211 is driving 3 x IAUT300N08S5N012 mosfets in parallel via independant 10 Ohm gate resistors. Please see the layout of the UCC27211 below. There is a lot if bulk capacitance in the system and I have a lot of decoupling capacitance at VDD Pin1. The switching signals seems to be okay without the motor connected but as soon as the PWM is started with the motor connected the IC fails immediately with a burn mark right next to PIN1. What can I do to diagnose the problem?

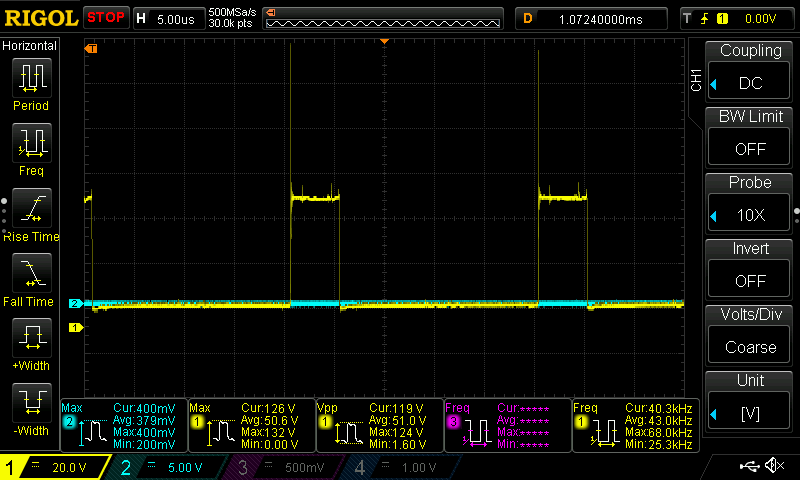

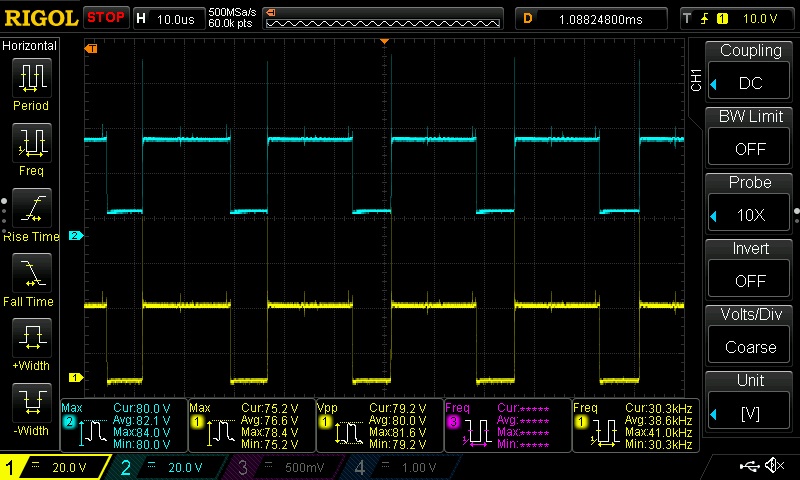

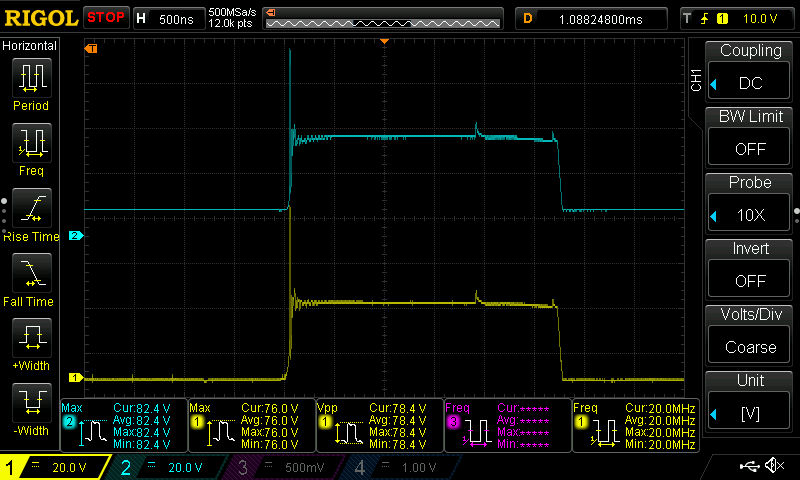

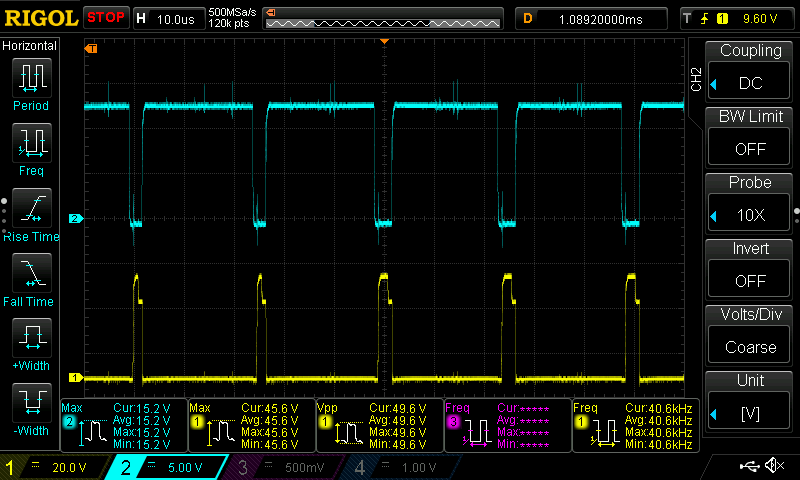

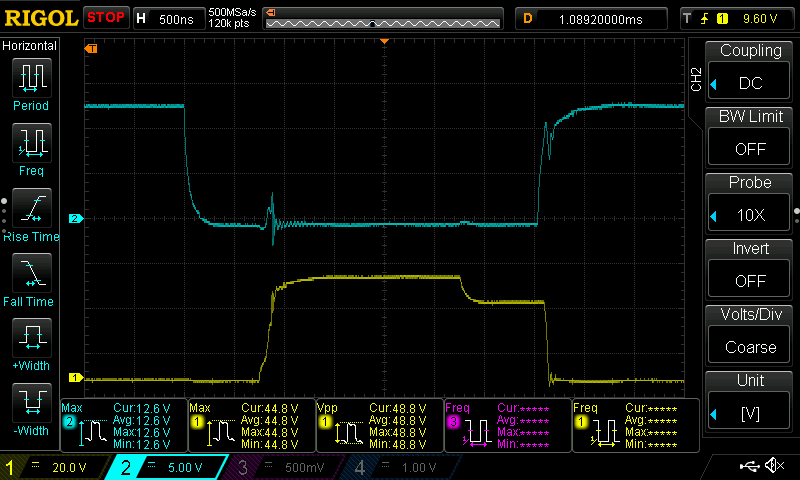

I have attached scopes of the inputs of the UCC27211 HI and LI pins, as well as the input at one of the mosfet Gate pins on the High side and Low side. The frequency is 40 Khz. I am using a 50V 1uF cap similar to the TI reference design: TIDUCB6, although they are targeting lower frequencies.

One thing to note: At the time of failure the battery voltage was quite low, I wonder if sudden shut-off could have anything to do with it?