Tool/software: WEBENCH® Design Tools

TPS548D21:

we have used TPS548D21 into our design, below are the specifications.

Input = 3V-13V, Typical voltage 12V+/-8%,

Output = 0.82V@ 40A (max), Typical current 25A.

Input is always 12V+/- 8%, only during Power OFF case, we will connect Backup power which 3V - 4.6V and during backup time of ~25 seconds Max current will be ~6A.

Currently we are doing minor changes in the design to re-design for lesser current where we can reduce few Input & Output capacitors to save BOM for low power designs.

So, Output will be 0.82V@25A with Typical current 15A, all other specifications will be same.

Now, I have few questions on Webench simulation on this.

1. For Balanced configuration in Webench, I see FSEL down resister is always coming as 37.4K, we have initially used 22.1K, But as per Datasheet Table 2 for Our Vin,Vout = <12V,0.82V> Duty cycle will be ~7% as per Table 7 it should be 16.5K with 7uS Time constant. there is a variation, which configuration to go( RFSEL – 16.5K(D=5-7.5)/22.1K(D=7.5-12.5)/37.4K(D=>21) )

One more thing to be noted, during simulations I saw Vout deviation for a load transient is less with 37.4K always(checked with 22.1K and 37.4K).

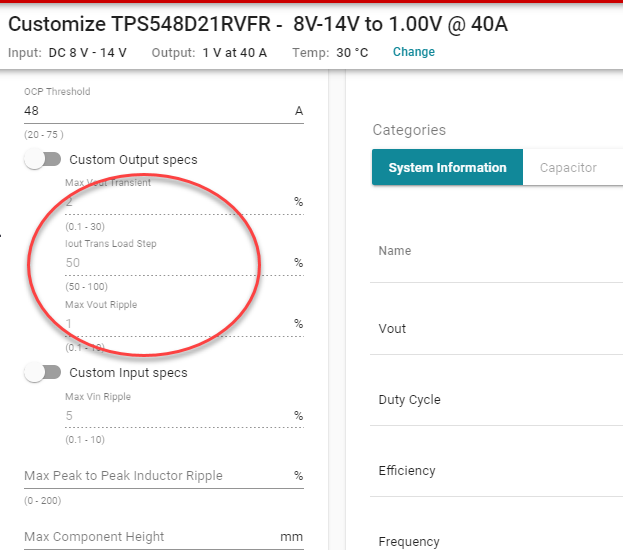

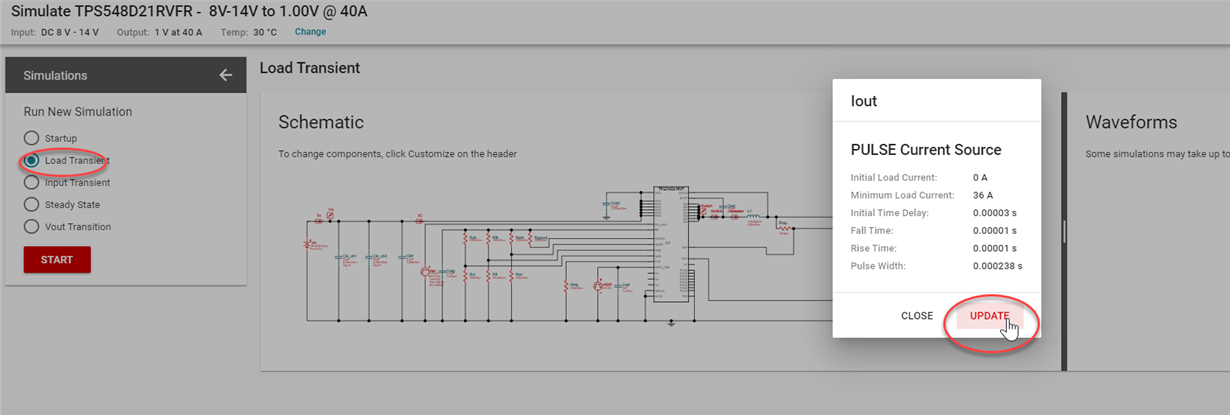

2. Is there anyway I can change the Webench simulation parameters to simulate Load Transient of 20-30% - Currently it allows only 50-100%.

3. For 0.82V @ 25A with Typical current 15A, I am going ahead with Below Input, Output capacitor combination

|

|

0.82V@40A (old) |

0.82V@25A(new) |

|

Input Capacitors |

12x22uF,1x0.1uF,1x2.2nF |

6x22uF,1x0.1uF,1x2.2nF |

|

Output Capacitors |

10x100uF,7x150uF |

7x100uF,7x150uF |

I am not seeing much difference in the simulations and as the simulations are for 50% load transients they are violating 2.5% tolerance for all cases, I don’t have way to test 20% Transient configuration.

3a. Is there any way to access 20% load configuration from 50% Load transient results approximately.

3b. With this New Input & Output capacitor configuration Do you see issues.

4. Is there anyway we can access Stability checks in Webench, I will get data in SwitcherPro but I am not seeing much data on Webench regarding stability.