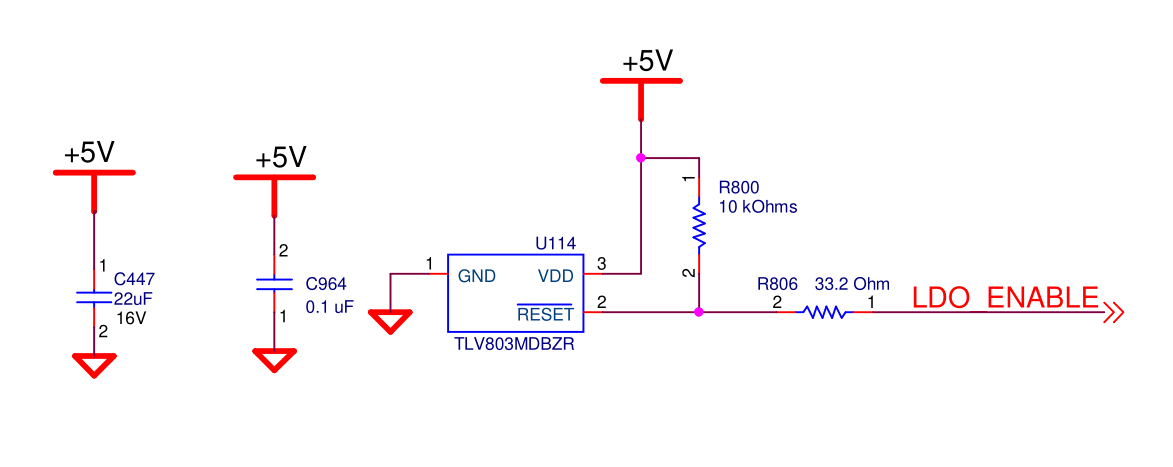

I am seeing in several TLV803MDBZR parts from the same batch that the rising threshold is at about 5.04V. Falling threshold is about 4.27V, which is within tolerance by the datasheet. Unfortunately 5.04V is too high for our system power supply. According to the datasheet, the hysteresis for this part should be 60 mV typical, although I don't see a max spec Another thread said that the maximum rising threshold should be more like 4.54V. In any case I would not expect VIT+ to be so high. Are these parts defective, or is this an expected behavior for the TLV803M?

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.