HI,

I'm using DCR010505U to generate a isolated 5Vout with a 5Vin.But we found some failure issues.

Some DCR010505U has no output, the fail rate is 2~3%;

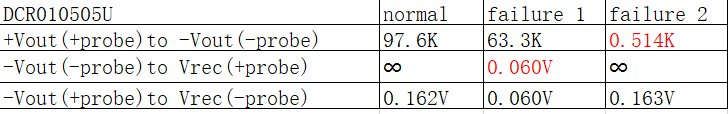

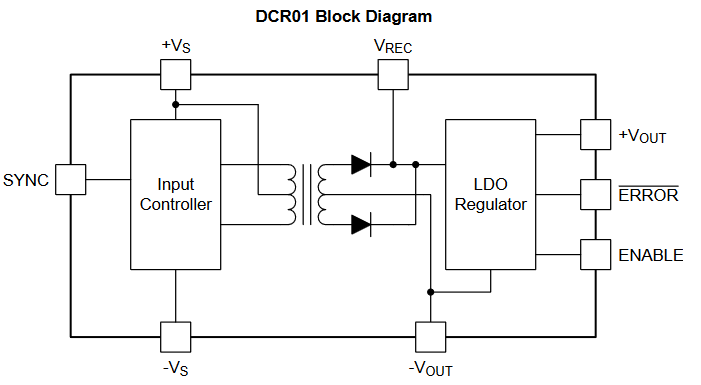

The input voltage for the normal DCR010505U is about 5.05V, then the Vrec pin is about 6.97V, the output voltage is about 4.98V.

I was wonder about the voltage on the Vrec pin,does about 6.97V is the right voltage?

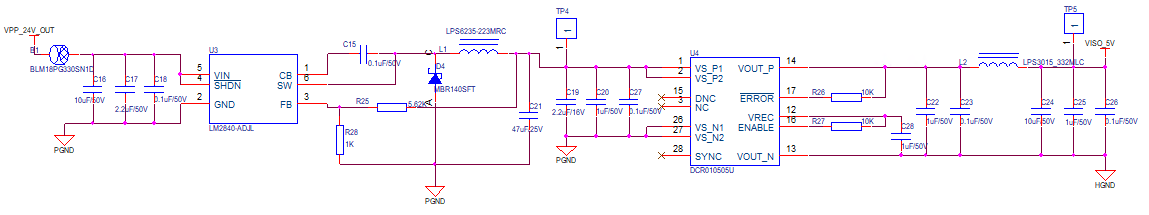

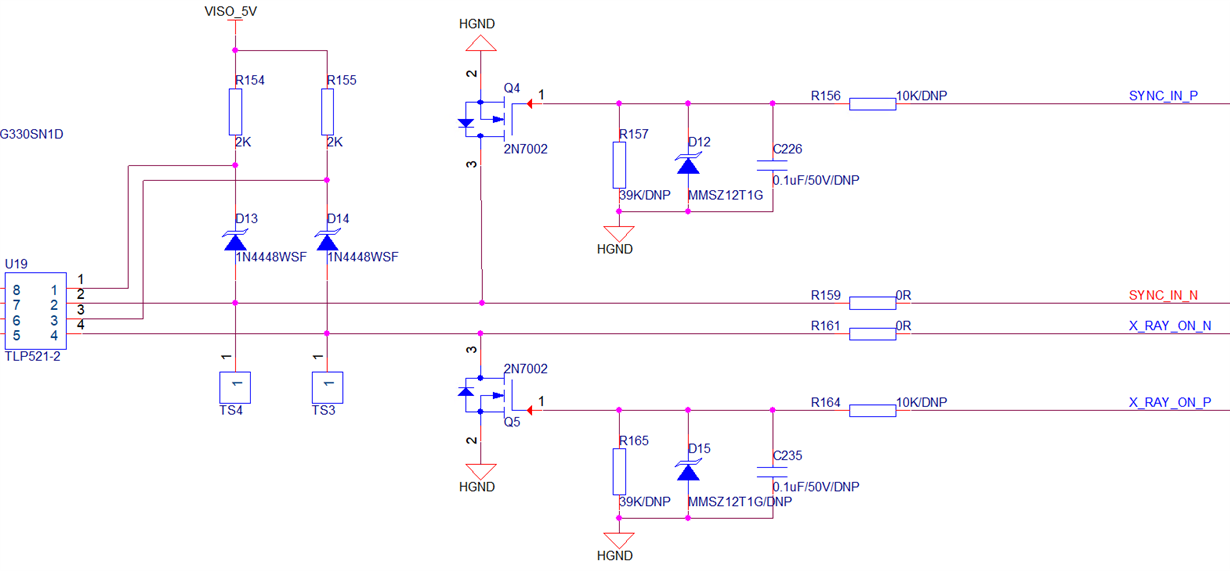

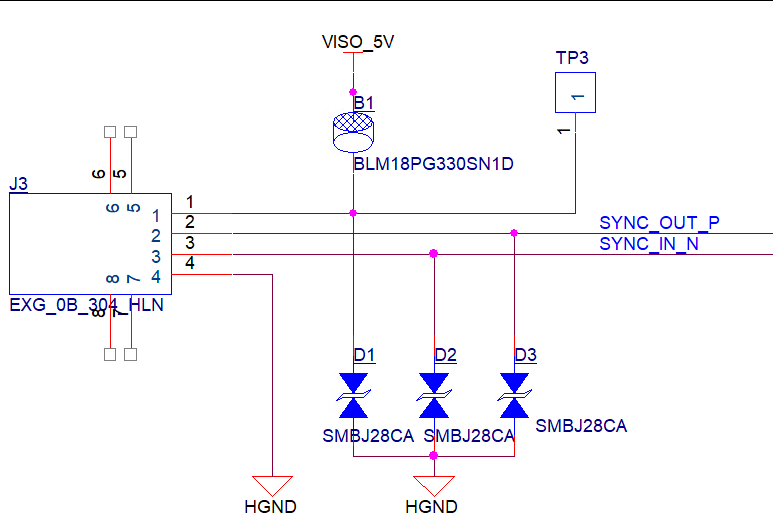

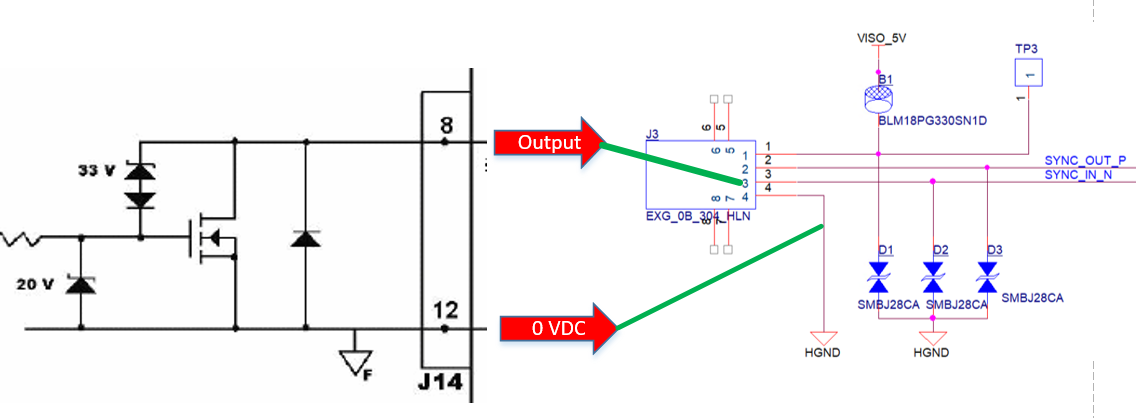

The schematic is showed as below, Whether need add dummy resistor to have a "preload" at the output?

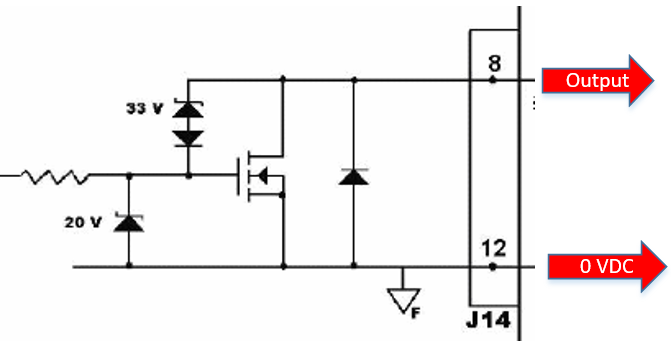

We test the failures DCR010505U,the results is showed as below, it seems like the inner LDO failure or the diode is damaged,

Would you give me some possible influencing factors?