Other Parts Discussed in Thread: PMP10555, PMP20080, TPS544C20

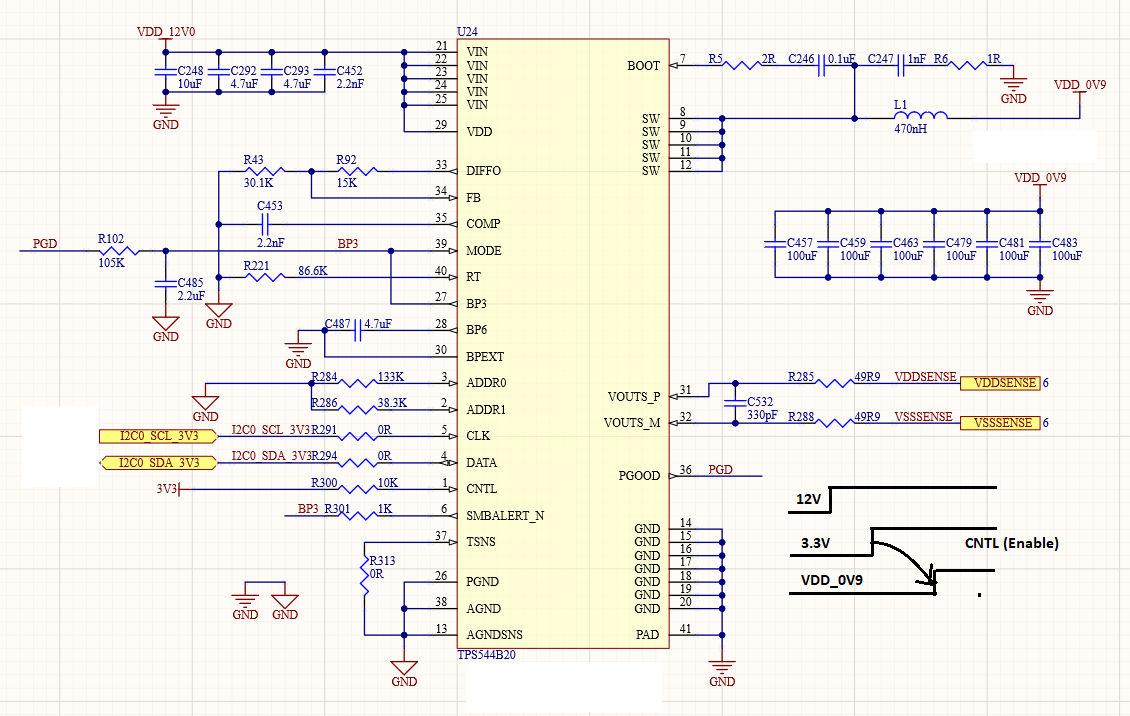

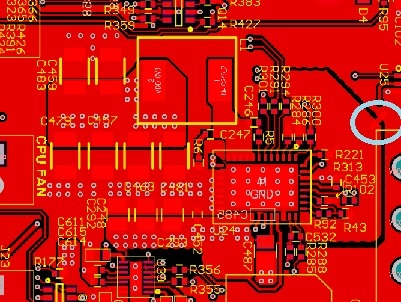

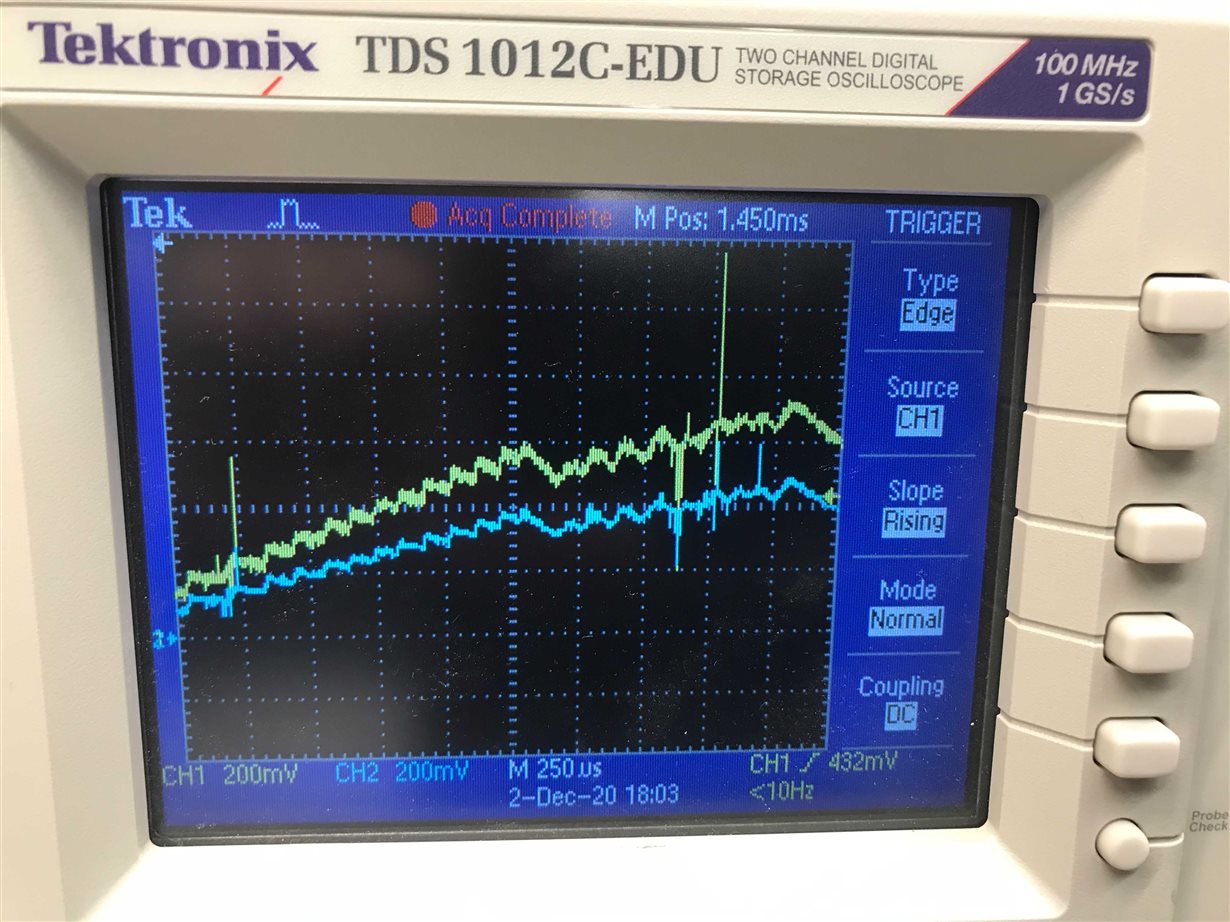

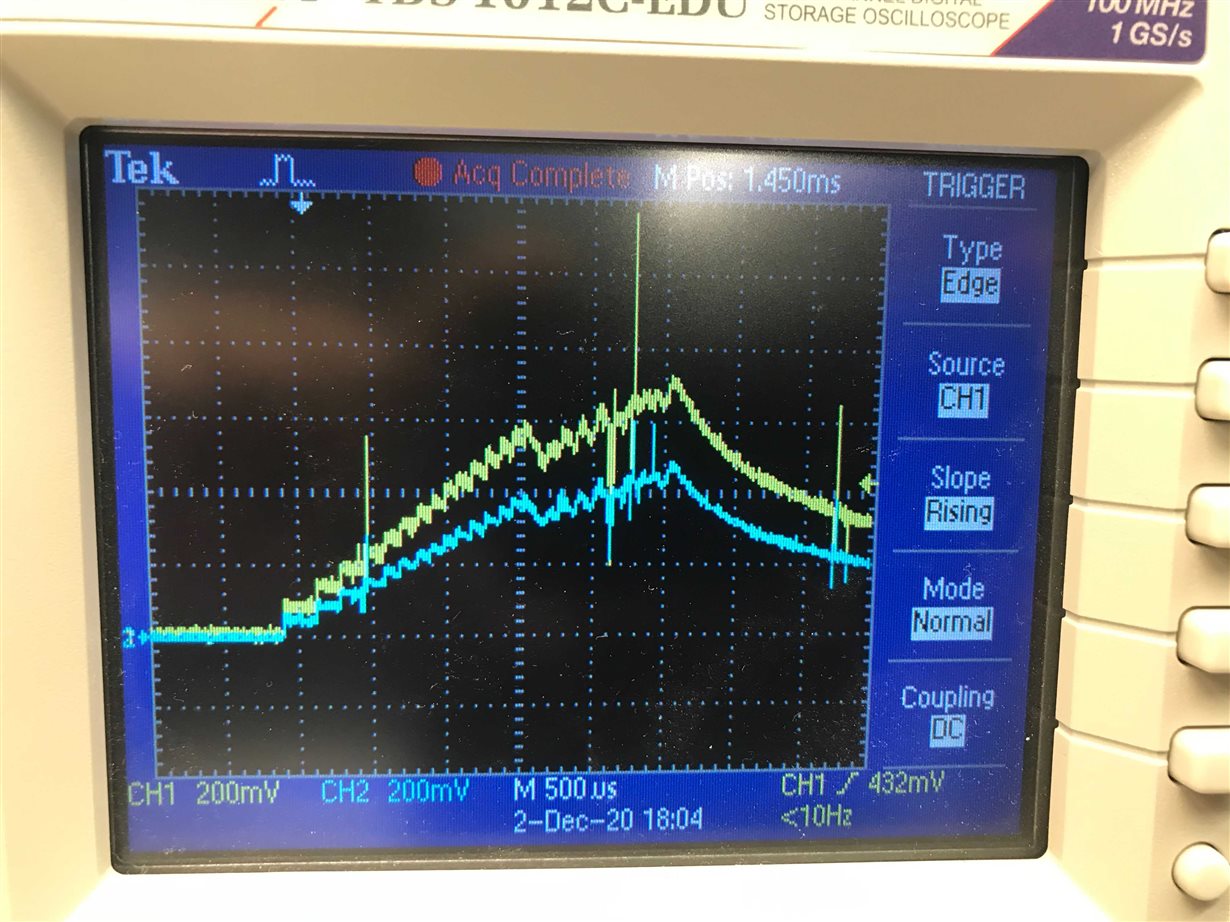

We are using TPS544B20 as regulator for core power (0.9V @ 10A) for our processor. The schematics was referenced from TI Webench online tool. All layout guidelines are followed. The regulator is enabled for sequencing uses CNTL pin of TPS544B20. We are facing issue on power up where we are not seeing the regulator turning ON. We are debugging the issue and want TI experts to check the schematics and indicate any observations. The CNTL is used to enable the regulator and this is connected to 3.3V with 10K as pull-up, which comes first then enables TPS544B20.

Please check the schematics and let us know your observations.

-Naveen