Other Parts Discussed in Thread: LM5155

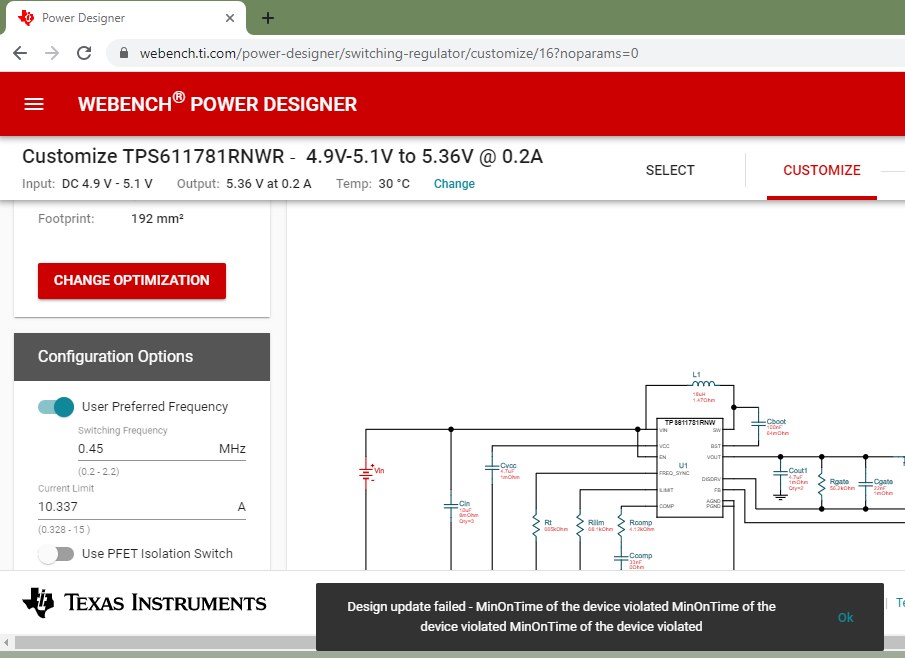

I saw a related question regarding Vout close to Vin. In my situation I have Vin = (4.9 to 5.1), Vout = 5.36 @ 200 mA. Will TPS61178 versus TPS611781 cause different results in Vout?

We originally wanted TPS61178 but this was out of stock so ordered the TPS611781. A colleague reports abnormally high Vout (about 5.9) and the FB pin is at 1.32V on one board.....not debugged yet. Normally if violating minimum on time (with many boost ICs) I would expect pulse skipping but perhaps this device cannot do that (??)

Similarly; should I expect any impact in Vout (with minimum pulse width violation) if the TPS61178 or TPS611781 is synchronized to an external clock?