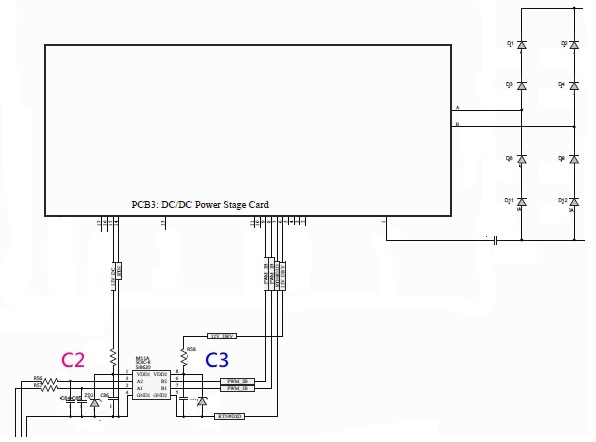

Other Parts Discussed in Thread: UCC27282

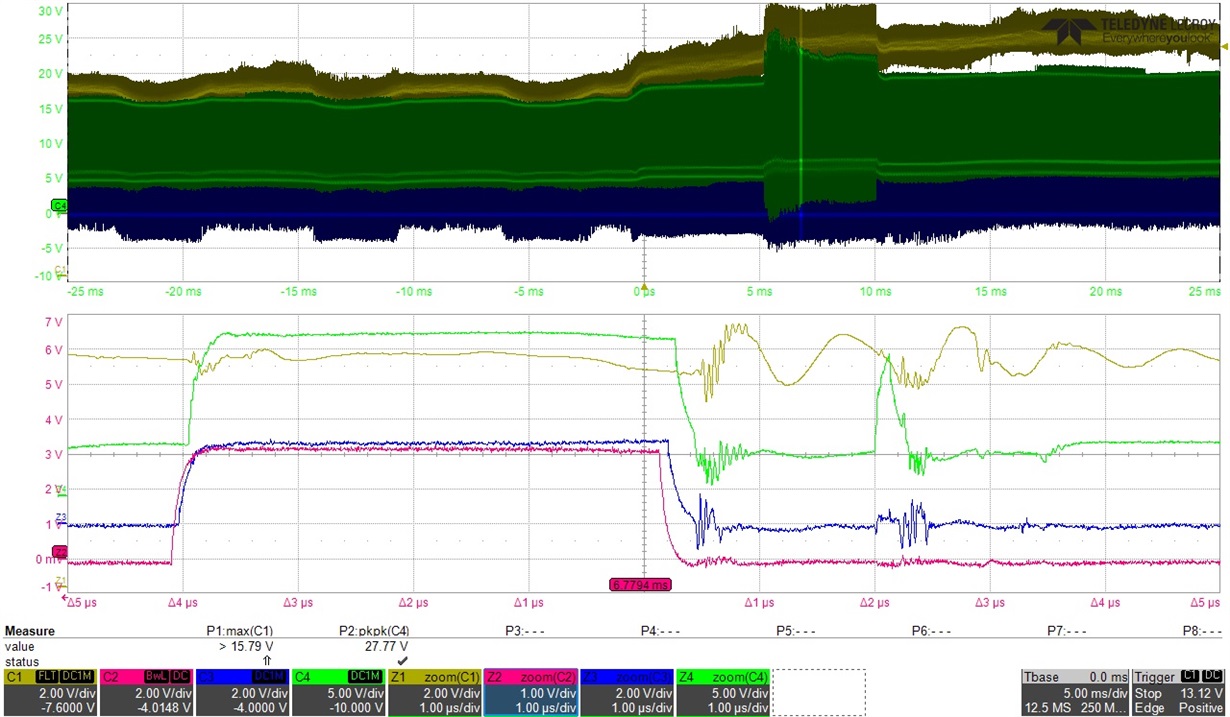

During the experiment, an abnormal waveform of the IC was found.

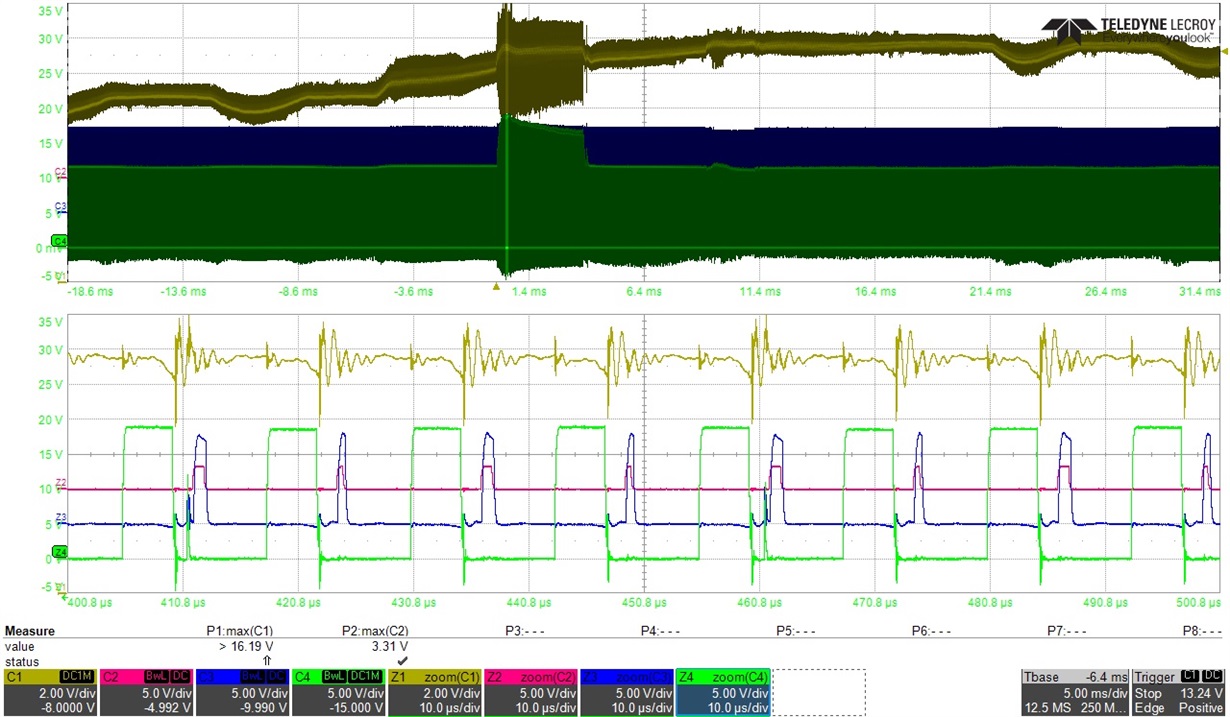

The test condition is input 11V to 14V, and the Vcc of the Driver IC is provided by the input.

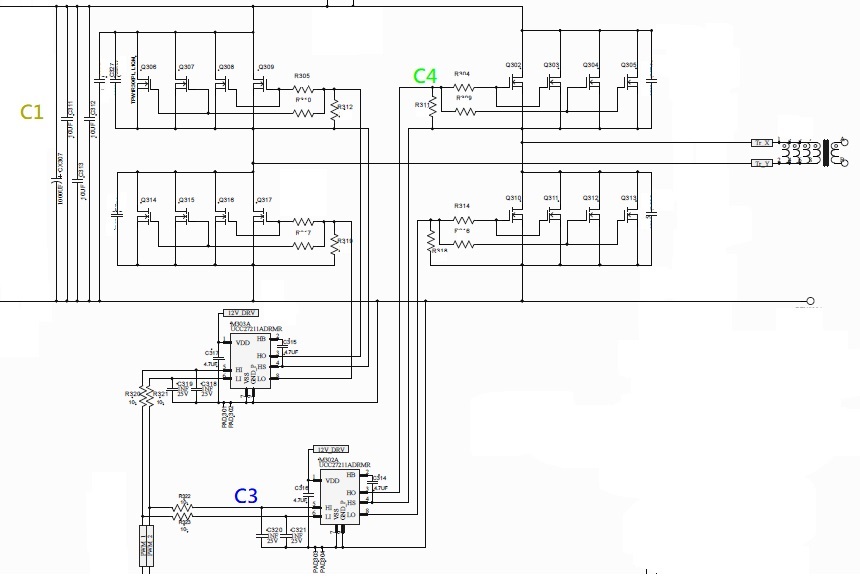

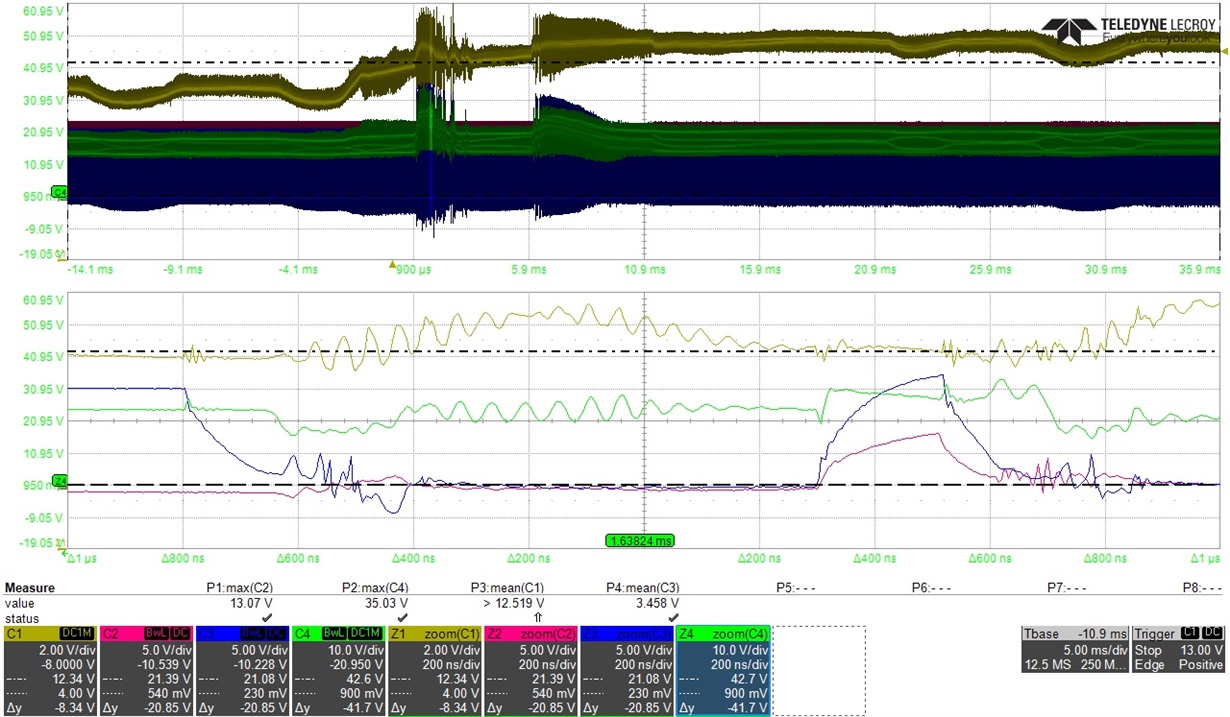

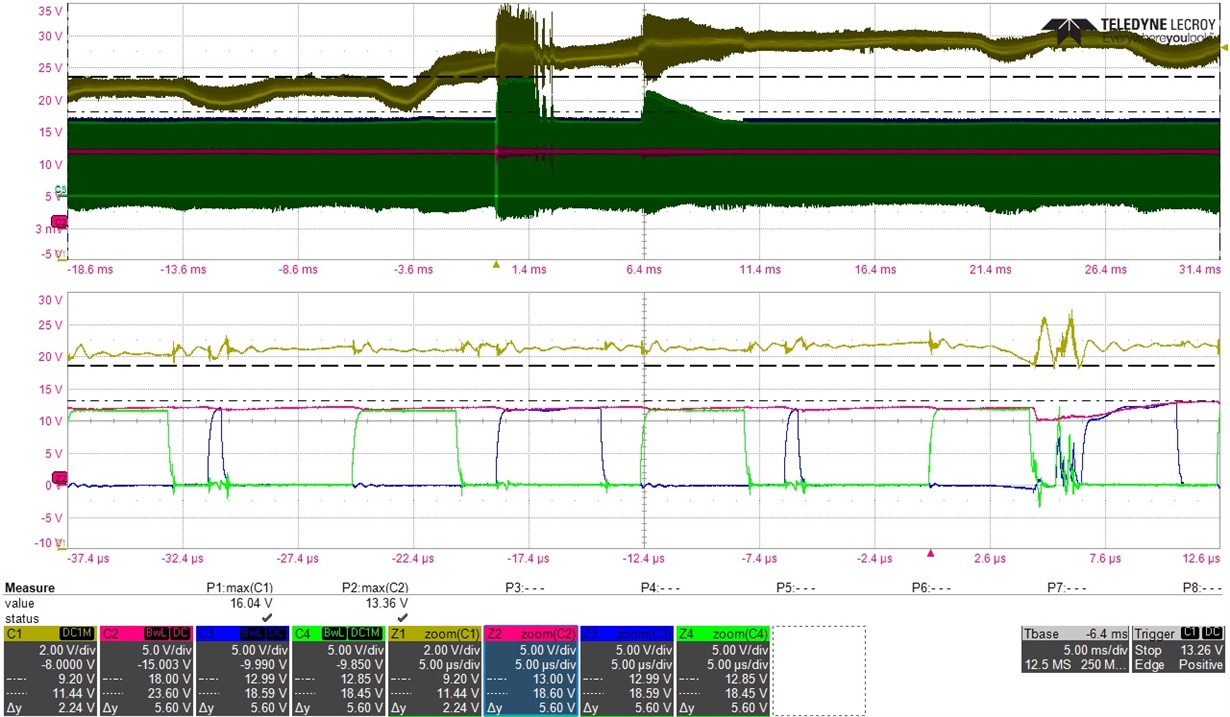

Measure the waveform along the circuit, respectively measure C1: Input voltage, C2: DSP Output, C3: Isolated IC , C4: MOS Vgs (after Driver)

The waveforms are as follows:

(C1:Vin, C2:DSP PWM, C3:Isolater IC to Diver, C4:Diver to MOS )

The result is as follows:

1. When Vgs is abnormally high, the DSP PWM is almost 0V, and the signal passing Isolated IC is slightly upward, so it should not be a problem with the DSP program.

2. From the previous cycle of PWM, it can be seen that the timing is DSP to Isolated IC to Vgs. It is reasonable to have a little delay time through an IC.

3. However, the Vgs of the abnormal waveform occurred slightly earlier than the Isolated IC signal, so it is judged that the problem may be caused by the abnormality of Driver IC.

Questions:

1.When the input voltage changes (11V to 14V), will be the Driver(UCC27211) affected? or other possible causes of abnormal waveform.