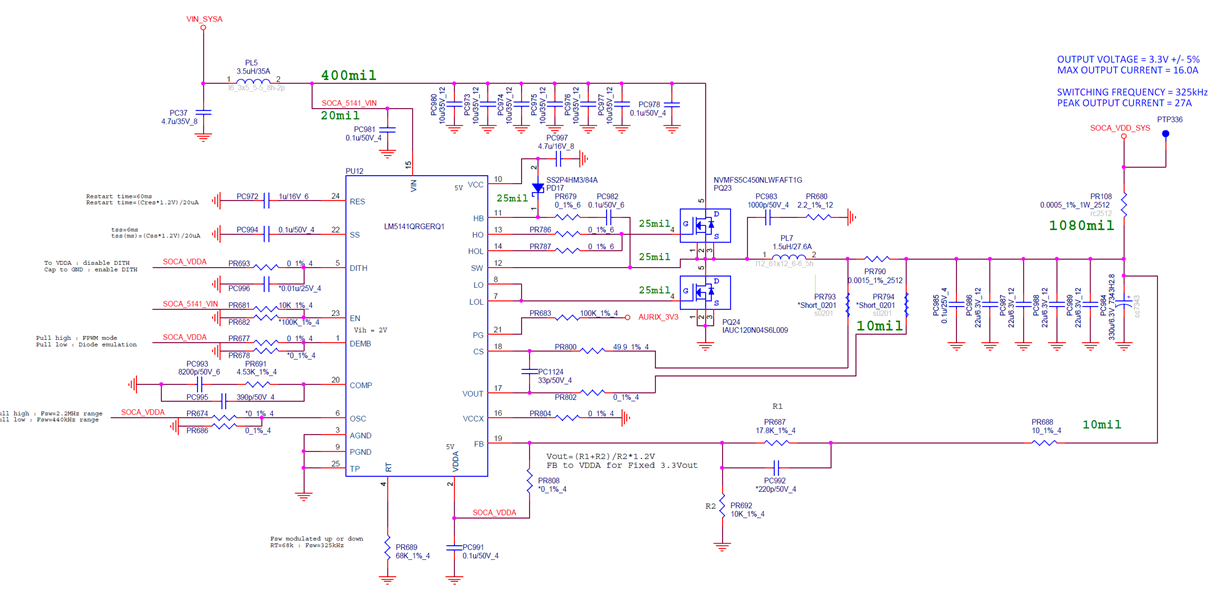

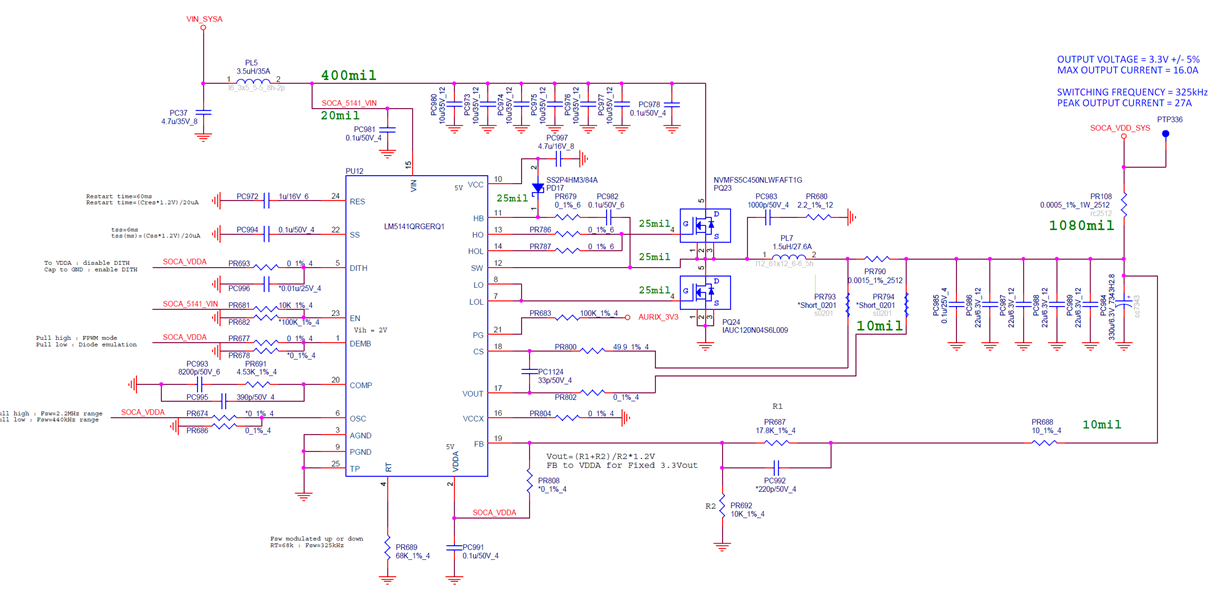

12Vin to 3.3Vo design:

I use electronic load and set it be CC-mode to do OCP verify.

I add load slowly from 2A until hiccup OCP, and then to eliminate the load (return to no load) --> But

Vo become to 5V??

Vo become to 5V??

How can I solve this issue?

Thanks.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

12Vin to 3.3Vo design:

I use electronic load and set it be CC-mode to do OCP verify.

I add load slowly from 2A until hiccup OCP, and then to eliminate the load (return to no load) --> But

Vo become to 5V??

Vo become to 5V??

How can I solve this issue?

Thanks.

Hi Eddie,

Please send a completed LM5141-Q1 Excel quickstart file for this design (the file is available in the product folder).

I noted that the IAUC FET from Infineon has a 4.2V Miller plateau (see Fig 15 in the FET datasheet). This is very high relative to the 5V gate drive voltage and may result in adequate turn on. Please change to a lower threshold FET and retest (for example, use the same device as the high-side FET as this has quite low Rdson as well).

Also, you need some damping after the 3.5uH inductor. Use an electrolytic cap (Cdamp = 4 x Cin ceramic, derate the nameplate value for voltage) and a resistor in series = Rdamp = SQRT (Lin/Cin).

Regards,

Tim