Other Parts Discussed in Thread: UCC28C43

Hello,

In the UCC28c43 datasheet ,COMP pin high level typical output voltage is mentioned as 6.8V, why it is greater than 5V (which is internal supply)

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello,

In the UCC28c43 datasheet ,COMP pin high level typical output voltage is mentioned as 6.8V, why it is greater than 5V (which is internal supply)

Hi,

COMP Abs Max specified as 6.3V (I suspect 6.8V in your message is actually 6.3V, otherwise let me know where is 6.3V you find in the datasheet.), is its maximum voltage that this pin can tolerate without damage. COMP pin can be connected external circuit so its abs max voltage needs to be specified and does not have to be the same as VREF.

Here whether it is 6.3V or 6.8V, it is the output voltage of error amplifier. Is the internal supply voltage for the error amplifier is 5V (Ref voltage) or not? If yes why it is exceeding the supply voltage?

It specifies how much COMP pin can be on the pin since COMP pin can be connected to an external circuit which voltage cannot exceed 6.3V. If you use internal 5VREF, then COMP max is on VREF specs.

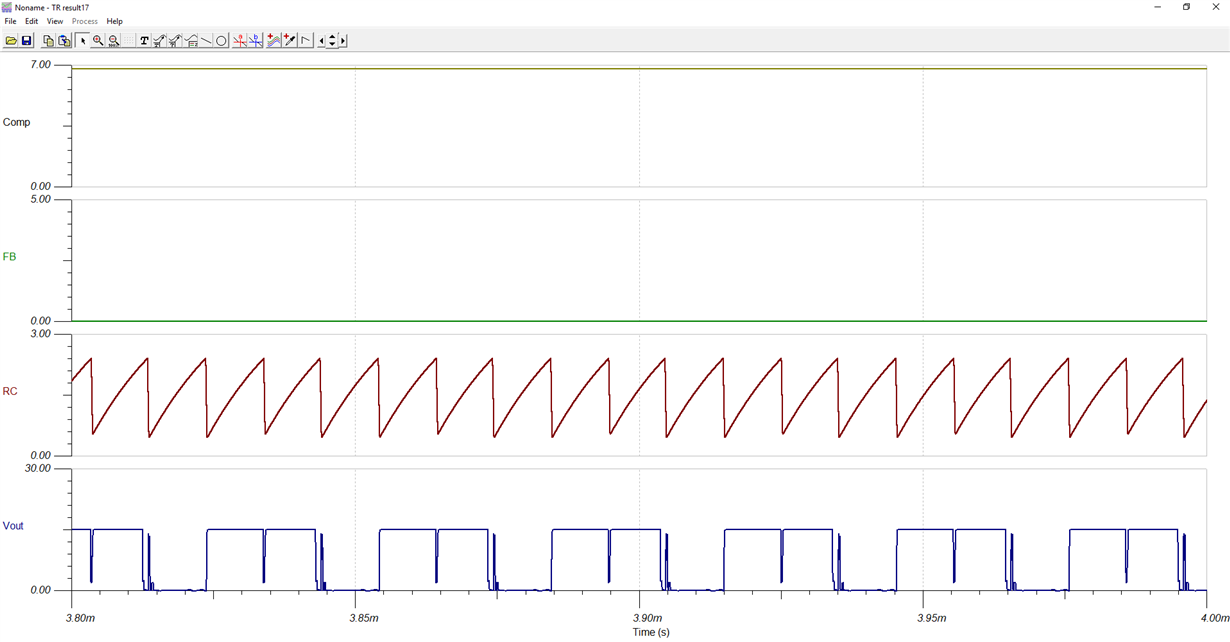

With the supply voltage of 5V, how the error amplifier output voltage is going to 6.3V or 6.8V. Because in op amps the max output voltage is either supply voltage or less than that. This is what i am asking in all the above messages. Even in TINA simulation i have seen the COMP pin voltage is 7V , when VFB pin is grounded. Please dont give your explanation on COMP pin max voltage capability, try to understand my question.

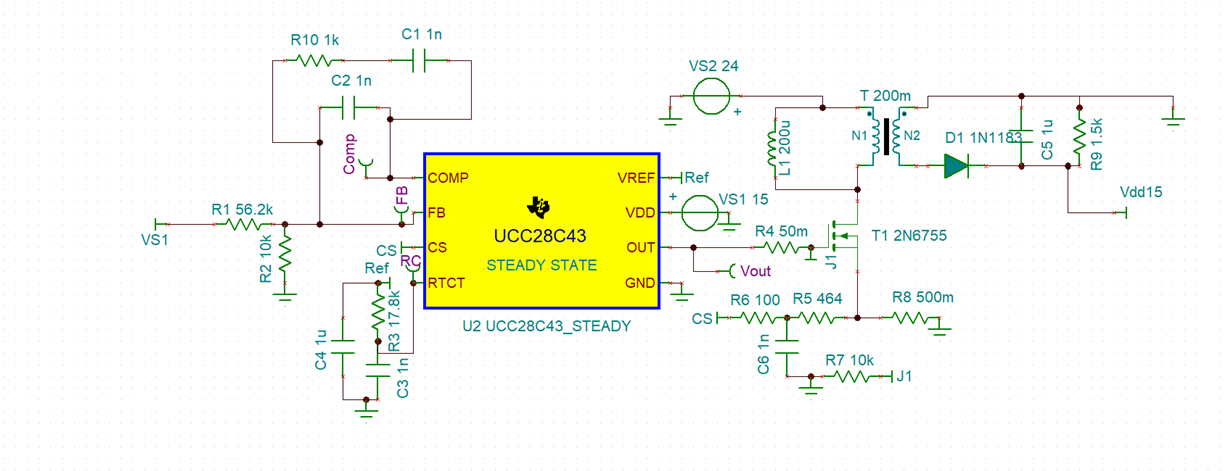

I have did a TINA simulation with below circuit. Here the FB pin is connected to a resistor divider(VS1 = 15V, R1=56.2k,R2=10k) ( FB pin voltage is 2.26V). I am attaching the TINA waveforms also.check the COMP pin voltage which is around 7V. here one more question is why the FB pin voltage is becoming 0V (it should be 2.26V as per resistor voltage divider equation)

Hi,

Note Tina model is created on Datasheet so if Datasheet says COMP typical 6.8V then the model will set up it as 6.8V

The COMP should not be over 6.3V based on its abs max specs. So the Datasheet needs to make consistency correction.

Inside VREF bias the circuit.

Hi,

I suggest you use 6.3V of COMP for your external circuit consideration as COMP abs max is specified 6.3V. There is obvious inconsistency on COMP pin specs to fix. If COMP 6.3V specs cannot solve your design issues, please describe your issues, and it looks there is no meaning to continue discovering COMP pin why 6.3V or 6.8V as which will be needed to fix for datasheet correction.

The IC internal circuit is biased by VREF which normal value is 5V. Why COMP has specs of 6.3V, or 6.8V, we will find out and make correction in the next datasheet revision. For now, if COMP 6.3V or 6.8V shows issues on your design, let's focus on solving your associated design issues.

Hi,

The FB issue should be related to either the Tina model or your model circuit setup. You may send to me with the model of your circuit for a look if you like.

I just run the simulation , i am getting the same previous results, not matching with urs. How the FB pin is 2.5V in ur waveforms. I am intentionally making it <2.5 (2.26V) with external 15V, resistor divider.

Hi,

I used analysis transient to run your model and obtained the result. The FB, COMP, as well others will be settled down by the circuit especially the components between FB and COMP.

But i have not connected the output (Vdd15) to FB pin via resistor divider, means i am not regulating the output voltage. I have connected from VS1(fixed 15V supply) with resistor divider to the FB pin. please run the simulation like this.

I just connected from external battery 15V to FB pin via the Resistor divider. Now FB pin is not pulling to GND. thank u for help. But VS1 is how becoming zero. how to check this?

I do not know what VS1 in your circuit is (I think that is the question for you) and where you get VS1 to connect to R1. You just need to add a voltage sense probe to VS1 connection and run transient simulation you can see VS1 drops to zero and pulling down FB to zero.