Dir Sirs and Madams,

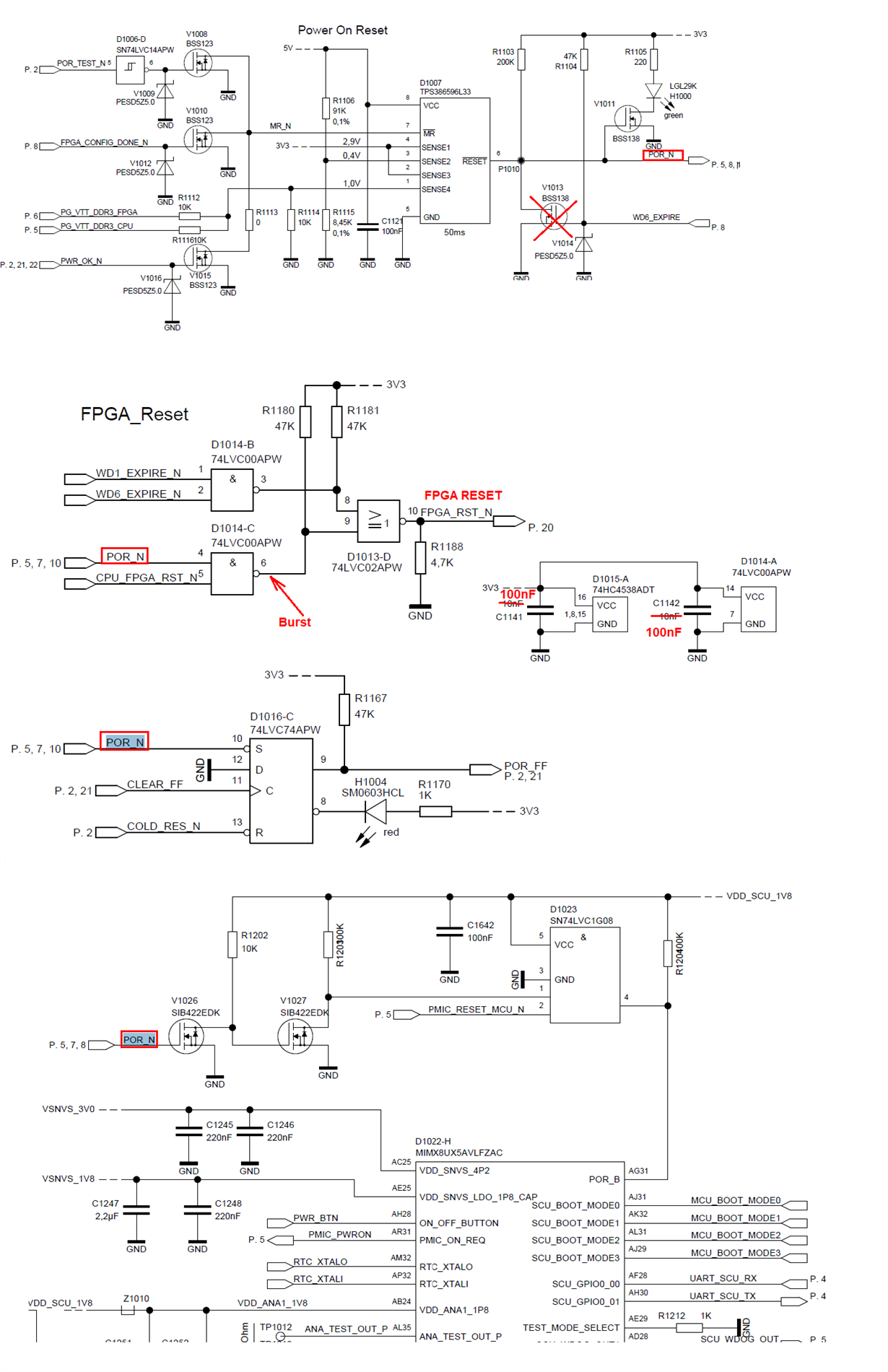

we are using TPS386596L33 as power supervisor. I have noticed some little burst at power up on output (pin 6, “POR_N”-Net) of D1007. That burst causes distortion making D1014 ringing at the output, which causes signal “FPGA_RST_N” ringing as well.

Removing output (pin 6) from net “POR_N” fixes that problem, but I also see that the voltage ramp looks different without D1007.

Adding a 10nF capacitor to the output of D1007 to GND makes a longer ringing behavior.

My questions:

- TPS386596L33 has an open drain output, and should not influence the voltage ramp, or am I wrong with that assumption?

- What do you think about that ringing (403MHz), I have done a lot of measurement, but still have no idea about the reason for behavior.

I also have done following changes to hardware, but without results:

- D1007: removing all MOSFET’s from D1007, decoupling all inputs with 10nF, increasing of blocking C1121, adding a LC filter to VCC of D1007, removing V1013, changing V1026 to a logic MOSFET.

- D1014-C: increasing of blocking C, adding a LC filter to VCC, R1180 as 10K.

Best Regards

Vitali Lach