Other Parts Discussed in Thread: , MLTLDO2EVM-037

Hi team,

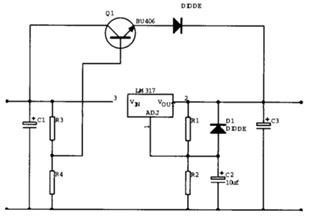

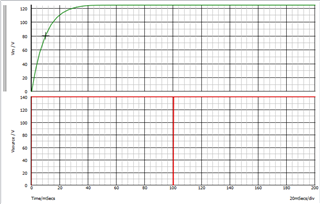

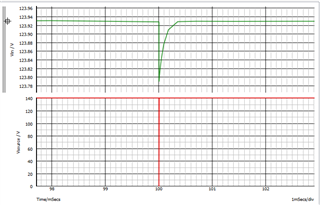

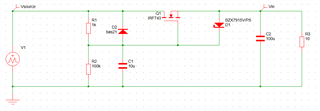

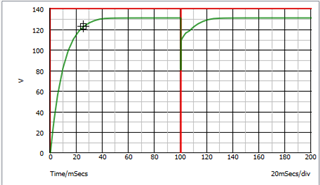

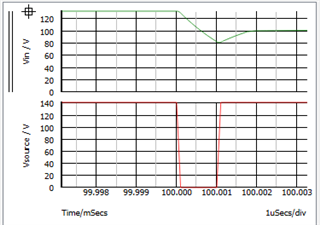

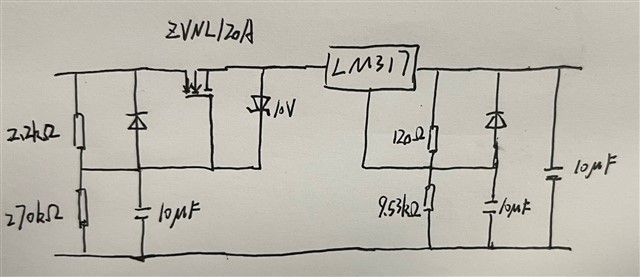

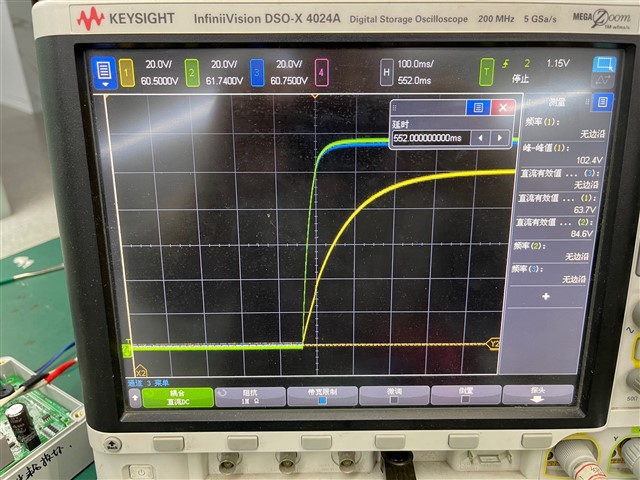

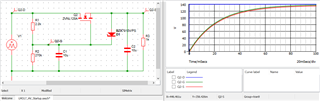

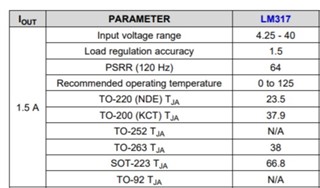

I am confused with the datasheet of LM317.In the first figure, we can see "In put voltage range" is up to 40V.

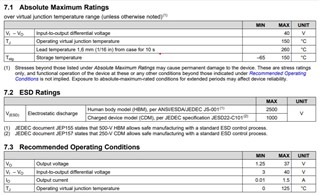

In the second figure, we can also see the "Input-to-output differential voltage max" is 40V. So I am wondering if Vinput can be larger than 40V. Is there something wrong with first "40V" for LM317 is floating?

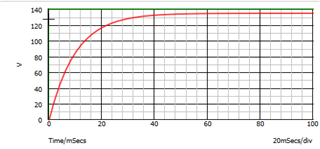

And in sheet 7.3 in figure 2. I want to figure out why Vo is limited within 37V for LM317 is floating. Are there any restrictions on Vo-Vadj?

Best regards,

Owen