Other Parts Discussed in Thread: UCC12040, UCC12051-Q1,

Hello,

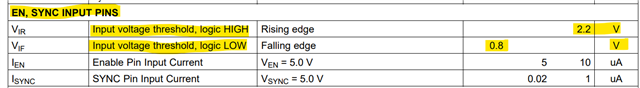

We would like to check whether the SYNC input pin can be driven with an external 3.3V clock signal, which seems feasible based on the datasheet.

Could you please confirm this?

Best regards,

Minkyun