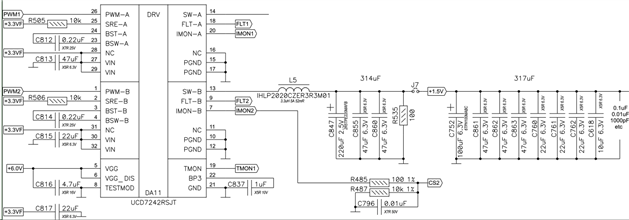

Other Parts Discussed in Thread: UCD7242

Hi Team,

I am using a combination of UCD9244 with two UCD7242 to supply power on my boards that are currently in production.

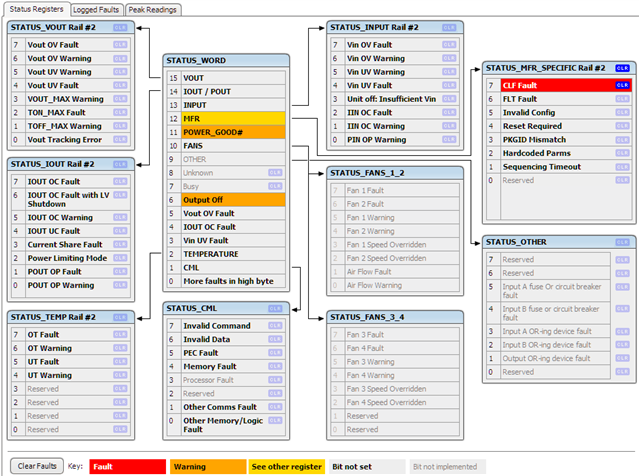

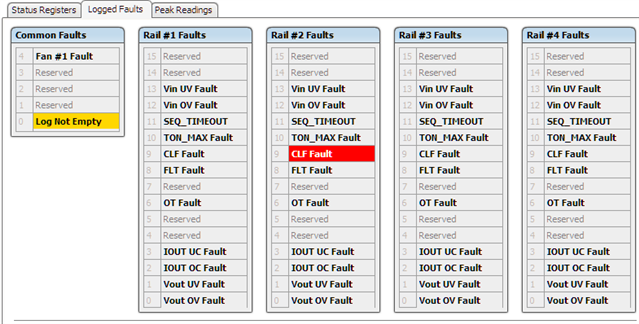

I have found that there are some (different) channels on some boards that fall to the overcurrent state (with CLF flag set) during the normal power off sequence initiated by the PMBus_Cntrl pin.

The "Fast Over Current Fault Limit" is set to recommended value of 150% (e.g. 4.5A for the Rated Current of 3.0A), and the real current consumption is much less than that rated current.

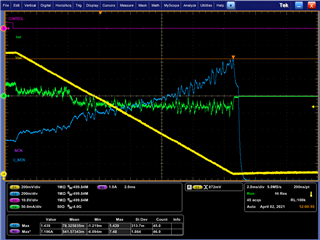

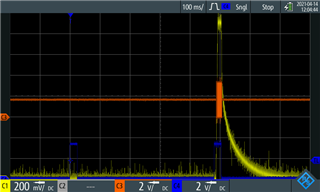

There is an example of the power off sequence for 1.5V rail with the "Fast Over Current Fault Limit" exceeded (CLF flag set):

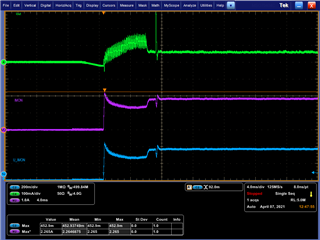

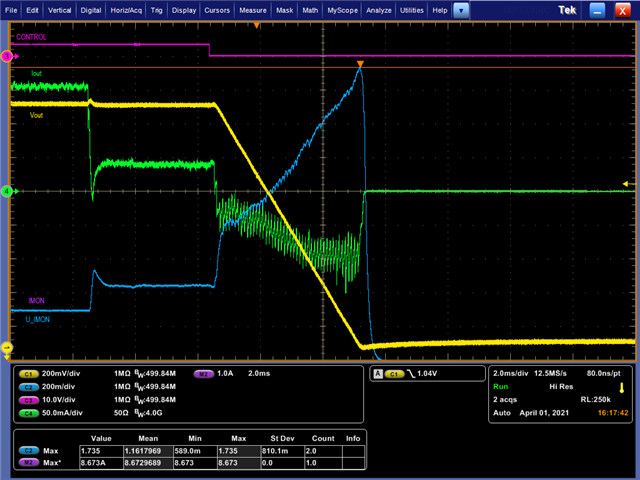

There is the power off sequence with "Fast Over Current Fault Limit" set to 9.0A (no CLF flag):

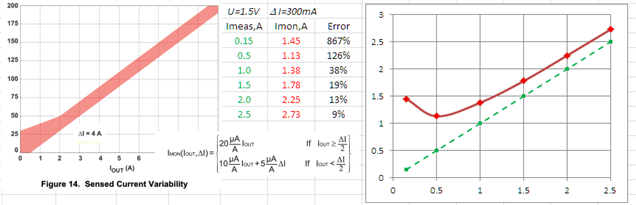

Ch2 is the voltage at the IMON2 pin and Math2 is the output current calculated as (U_IMON / 10kOhm) / (20uA/A).

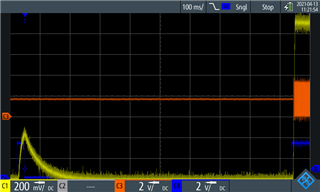

Ch4 is the current measured across the J7 jumper:

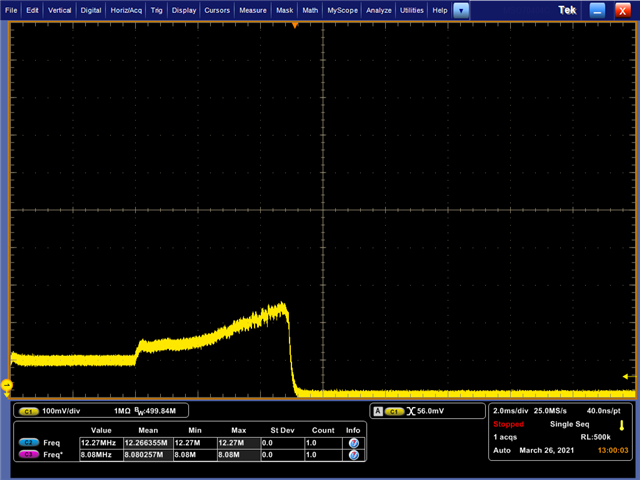

IMON voltage for the same rail at another board (250mV_pk equals to 1.25A_pk):

The project file for the UCD9242: PMIC_test.xml

Q1: Why there is so large current observed at the IMON pin of some UCD7242 channels during the power off? May it be e.g. due to very large error in reported current at low output currents?

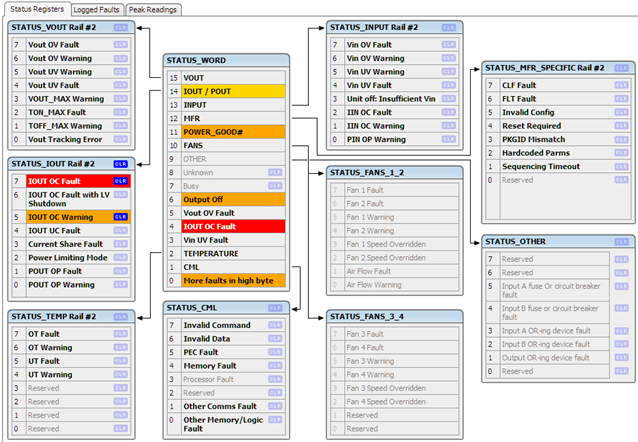

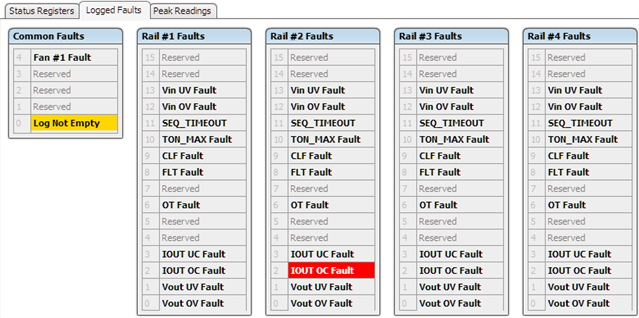

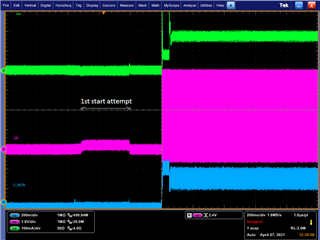

Q2: I am observing that the failed rail is not starting during the next power on sequence initiated by the PMBus_Cntrl pin immediately after that failed power off (other rails are starting as usual), and it starts successfully during the next power on attempt.

The rail always starts as expected when I am starting it individually with the OPERATION command, but when I am trying to start it with control pin (by changing the external voltage or by inverting its active level in UCD9244 register) or even by changing the "On/Off Config" setting to "Always Converting" - the rail does not start first time after the CLF bit was set during previous power off and it starts during the next attempt.

Is this an expected behavior?

(Vout<100mV during the unsuccessful power on attempt is due to leakages from the other power supplies)

BR,

Denis