Hello,

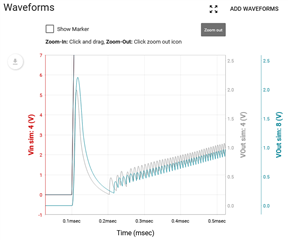

I'm trying to design a 4.2V regulator using the LM25085. I have run a few webench-design based "startup" simulations and, in each case, the simulation shows a significant output voltage overshoot at the very beginning of startup. The absolute max input voltage for my application is 4.8V. As you can see from the screenshots below, the overshoot in each of my simulations exceeds 5V. Is this overshoot "real" or just a product of simulation? If it is real, is there a way to reduce the overshoot so that I can be guaranteed it would never exceed my 4.8V absolute max input voltage spec?

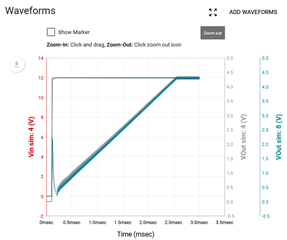

"Zoom Out" simulation view

Zoomed in simulation view

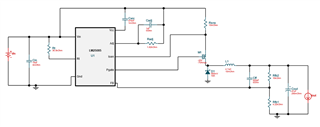

Simulated Webench design

Thanks in advance,

Paul W.