Hello!

I have some questions about how to make UCC27212's output function as datasheet.

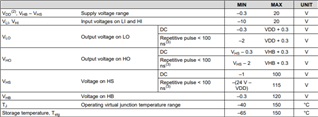

According to information on page 5, which says the maximum value for output VLO and VHO are VDD+0.3 and VHB+0.3.

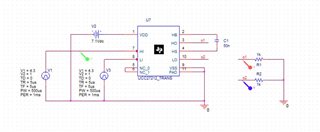

And here is my circuit and results of simulation in Pspice, everything seems right. VLO and VHO both almost reaches VDD(7V).

But when I test it in reality with the same circuit, I get an eccentric waveform. The next image is VLO, which is smaller than expectation obviously. VHO is nearly as same as VHS, so output of high side is close to zero. This waveform can hardly drive MOS.

Thanks

Auold