We are using the TPS23754 as POE application in one of our designs.

During the design phase, We used the TPS23754EVM_420 as reference designs.

/cfs-file/__key/communityserver-discussions-components-files/196/POE_2D00_PS.pdf

The POE output was set to 6.2V @ 3 amp max and we have to synchronize the POE to 650kHz.

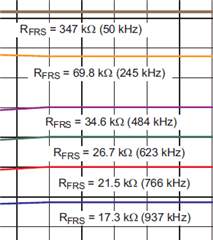

The max Switching frequency described in the datasheet is 278 kHz with RFRS = 68.1 kΩ , while higher frequencies are described for different RFRS values( see below).

Since in our design RFRS = 69.8kΩ the free-running Switching frequency is set to 245kHz.

We would like to confirm that our design supports the desired sync freq of 650kHz (without changing RFRS).

Looking in the datasheet we found that "The converter may be synchronized to a frequency above its maximum free-running frequency by applying short AC-coupled pulses into the FRS pin"

Furthermore, we didn't found any limitation on the F sync max pulse width.

Please advise if we can use 650kHz sync freq or that we would have to change RFRS or to use a lower sync freq.

Thanks,

Ohad