Other Parts Discussed in Thread: LP87702

Hi,

How long does it take for LP87702's Power GOOD to activate?

Is there a chance to shorten it?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi,

How long does it take for LP87702's Power GOOD to activate?

Is there a chance to shorten it?

Hi,

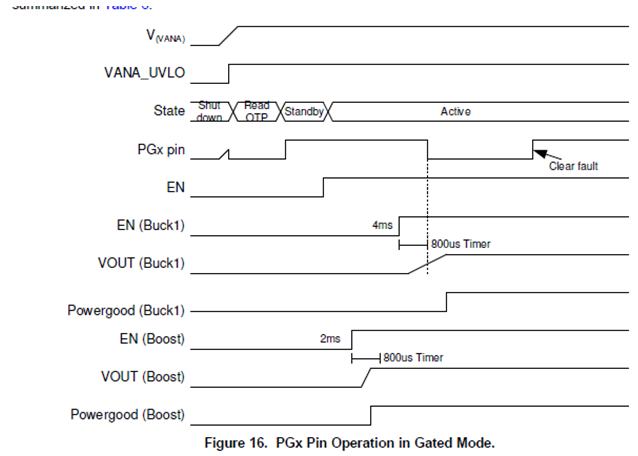

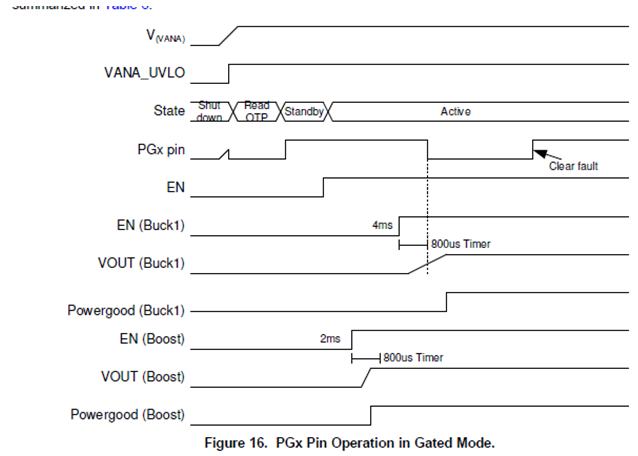

PG0_RISE_DELAY and PG1_RISE_DELAY fields in PG0_CTRL (0x18) and PG1_CTRL (0x1A) registers control the debounce delay of the powergood. From the picture it looks like the bit is set to 1 meaning 11 ms delay. Writing the bit to 0 shortens the delay to around 7 µs.

Best regards,

Samuli Piispanen

Hi Team,

From LP87702's PG0_CTRL (0x18) and PG1_CTRL (0x1A) Reset are 0h, but the actual power on measured is about 10ms, so customer would like to ask the root cause is OTP default of LP87702 is set to 1?

Hi Kygo,

The default reset value depends on the used OTP. For catalog LP87702K-Q1 and LP87702D-Q1 solutions the OTP defaults can be found from the following document.

https://www.ti.com/lit/pdf/snvu593

PGx_RISE_DELAY is set to 11 ms for both of the devices.

Best regards,

Samuli Piispanen