Other Parts Discussed in Thread: TPS546D24A

Hi Team,

My customer has PMBUS communication failure issue when using TPS549D22 (replace EM2260) with 1SG110HN2F43E2VG FPGA.

Question:

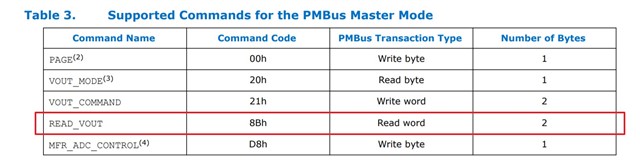

Does TPS549D22 have 8Bh register?

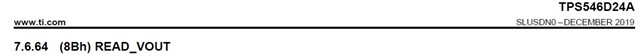

I find 8Bh in TPS546D24A but not in TPS549D22, why TPS546D24A has 8Bh but TPS549D22 doesn't have? what's the PMBUs difference between them?

The reason that I need 8Bh is because it's the power management requirement in the FPGA.

8Bh in TPS546D24A:

8Bh in EM2260:

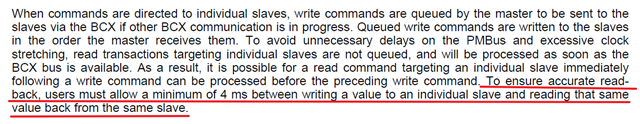

In the Intel® Stratix® 10 Power Management User Guide, it needs to read 8Bh register.

Best regards,

Yang