Other Parts Discussed in Thread: BQ78350

Hi,

I am using the BQ76200 with the BQ78350+ BQ76200.

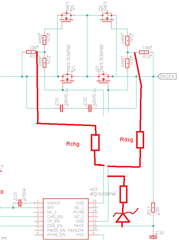

I am able to estabilish connection and turn on mosfets. I have tried testing the OCD cut-off. The cutoff happens as expected but the revival does not happen (maybe I am missing some configuration). However, after this event, post reseting the BQ78350, when the discharge is enabled and I connect the load (resistive) to the output of the system, the output voltage drops from the pack voltage to close to 0 V and the output voltage re-appears when the load is dis-connected. The partial schematic is attached for reference.

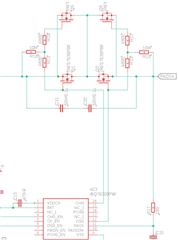

Realizing that the mosfets Q1 and Q2 don't have series resistors, I had removed the fets and performed the test.

I replaced the BQ76200 and mosfets were driven as expected. I then, retried the OCD cutoff and this resulted in the same behaviour as the last time. when the BQ76200 fails, I notice that the Vgs at the mosfet is about 1.5 V compared to 10 V when it works.

May I know if there is something I have missed and what could be the cause of this issue?

Thanks and regards