Hello Admin,

I have a question about using TPS548B22 for Xilinx FPGA.

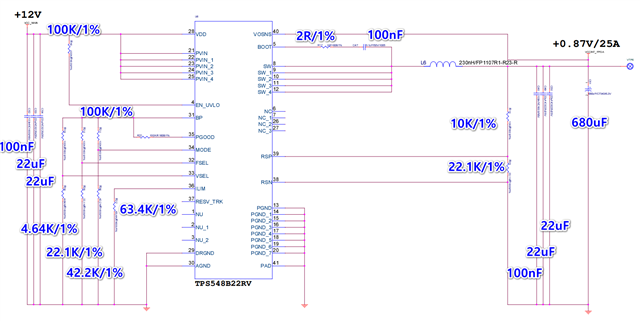

0. Web bench setting is like the below.

- Input: 12-14V

- Output: 0.87V

- Output current: 25A

1. Out circuit diagram is different from Web bench output and it always outputs 0.43V.

what's wrong with our circuit?

All things must same with Web bench, Such as input and output capacitor and any resistors?

2. How can I change my schematic for better performance and stable output for 0.87V?

Wait for your kindly reply

Thanks.