Hello,

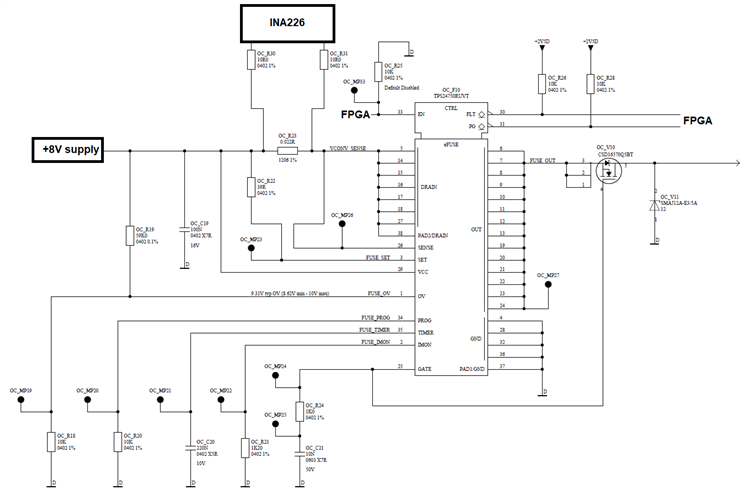

I am using TPS24750 on a 8V-1A application. During powering up the input of the Efuse (while keeping Efuse enable pin low) the fault output of the Efuse goes low for 2 microseconds before being released again. This occurs when Vin is rising and passing around 1.9V. I have 4 similar circuits. I see this behavior constantly in one, sometimes in another and never in other 2.

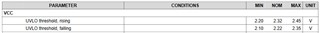

After this behavior, I am still able to enable/disable the Efuse. What can be the reason of this short fault indication? Datasheet states: "The FLTb pin does not assert if the internal MOSFET is disabled by EN, OV, overtemperature shutdown, or UVLO." Therefore I don't expect this behavior.

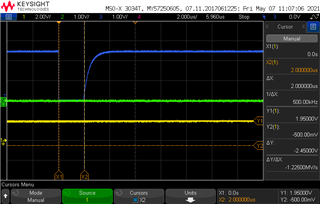

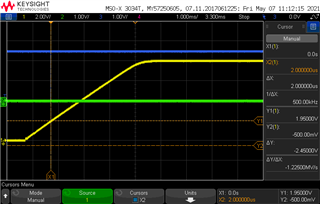

Oscilloscope picture:

- Probe 1: Efuse Vin

- Probe 2: Efuse enable pin

- Probe 3: Efuse fault pin (pulled up to +2.5V)

- Efuse output, IMON, TIMER pins are always at 0V during this behavior.

Condition:

- No load connected to Efuse output.

- Overvoltage limit set at 9.3V, power limit at 12W, current limit at 1A, trip time at 30ms.

Kind regards,

Zeki