Hi Team,

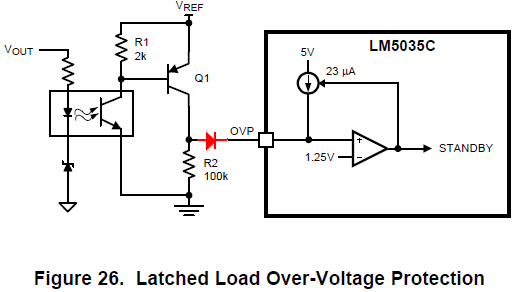

My customer considers to use "Latched Load Over-Voltage Protection" as Figure.26.

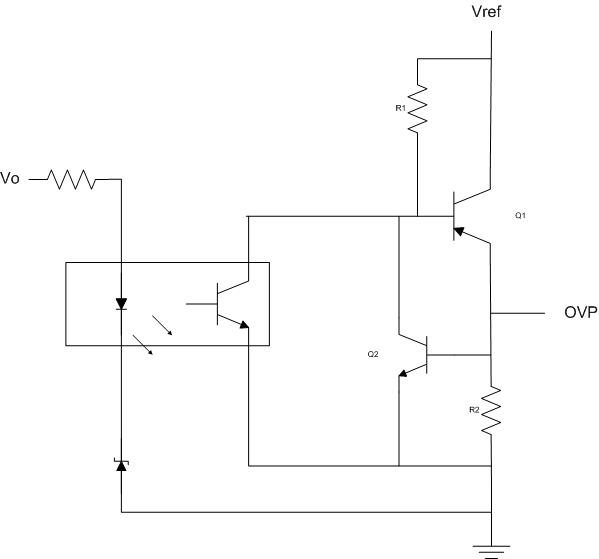

He would also like to detect two types of OVP failure by OR-ing connection.

Is it possible to put a diode as the following?

I concern if it can operate "Latched Load Over-Voltage Protection".

Best Regards,

Yaita / Japan disty