Hi Everyone.

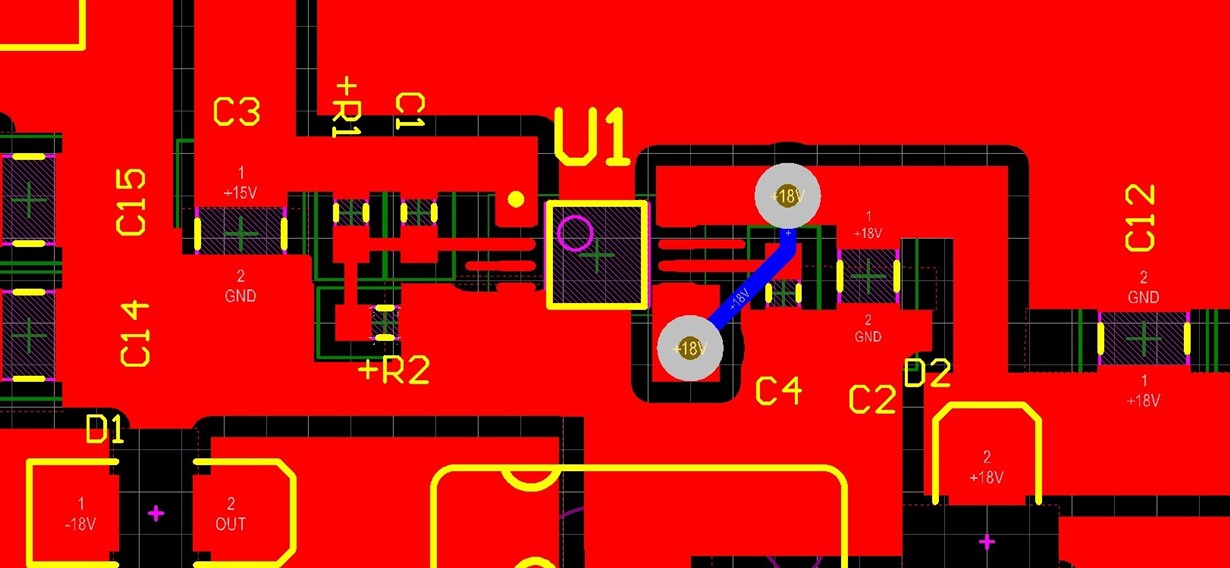

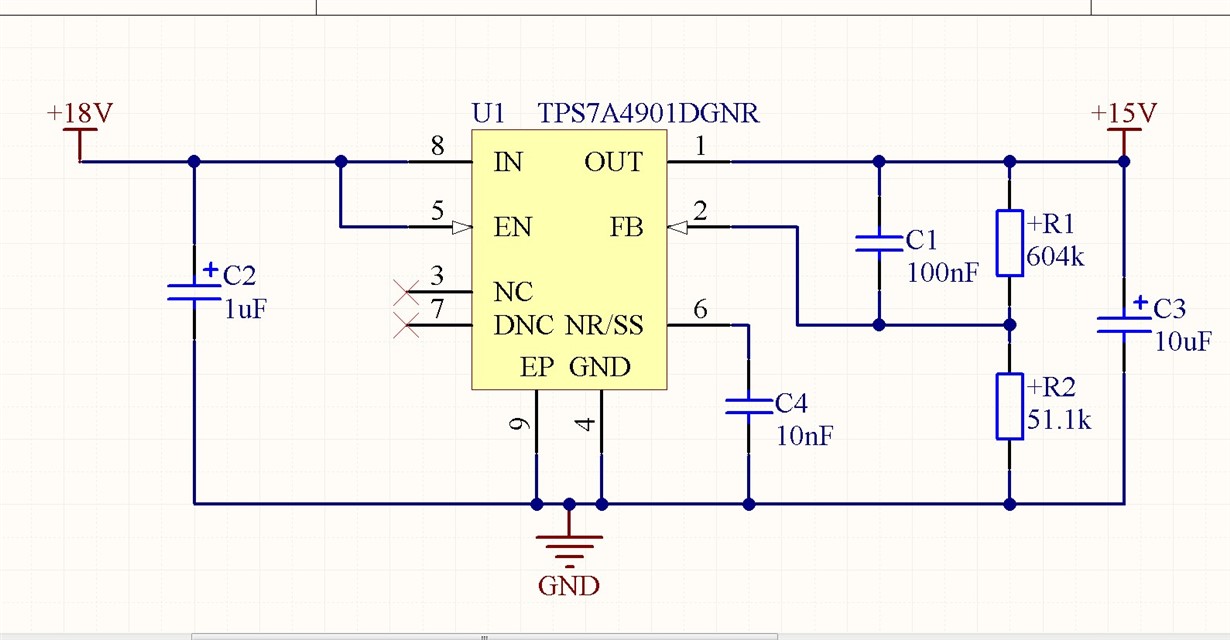

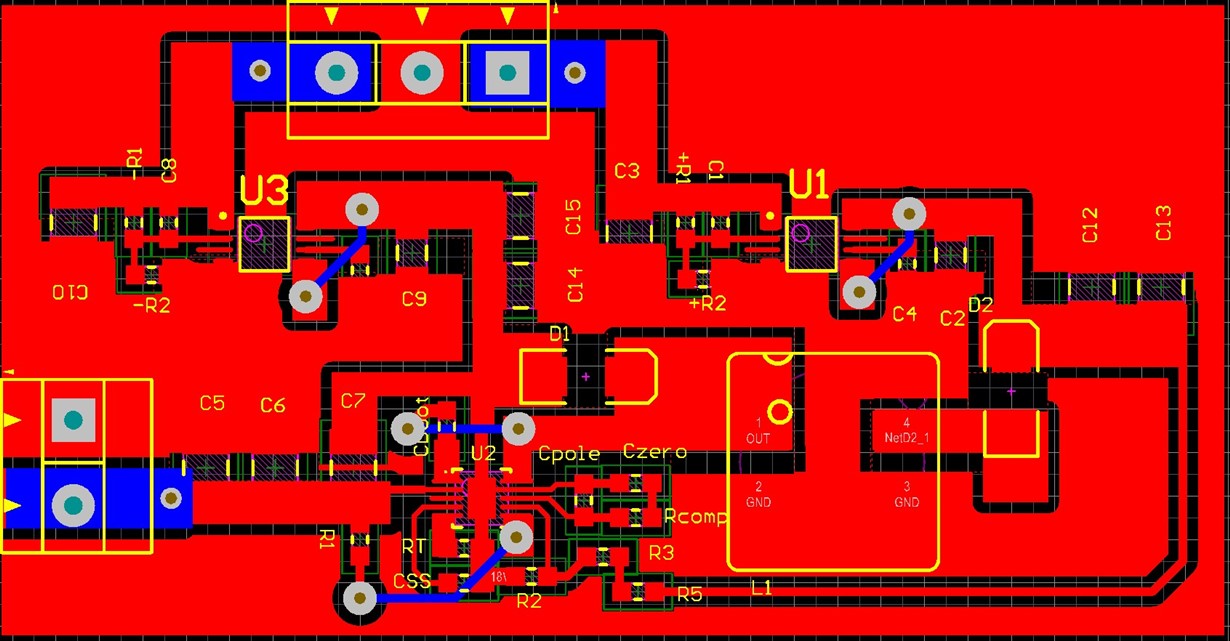

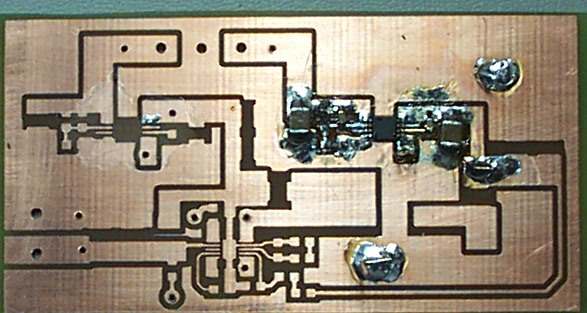

I have put together an eval circuit of the TPS7A4901, and with the exception of resistor orientation I have followed the PCB layout example of Figure 36 on page 20 of the data sheet, and the circuit diagram from Figure 9 page 12 of SLVU405.pdf (TPS7A30-49EVM-567). I set up the feedback network to give me Vout = 15V.

When I apply ~16.5V input voltage I get nothing at the output apart from an initial jump of the output voltage from about 5 to 10 volts and then a rapid decay to ~zero. If I remove Vin from the EN pin5, then the output shoots off to ~14V, and when I reconnect Vin to EN, the output voltage settles on 15V which is exactly what I want. The TPS7A30-49EVM-567 demo board gives the correct output voltage every time, as expected.

So why am I getting these results given my layout is as close to the recommended? is there something with this part I've missed? or something else I could do to sort it out?

Thanks for your help

Martin.

SLVU405