Hi team

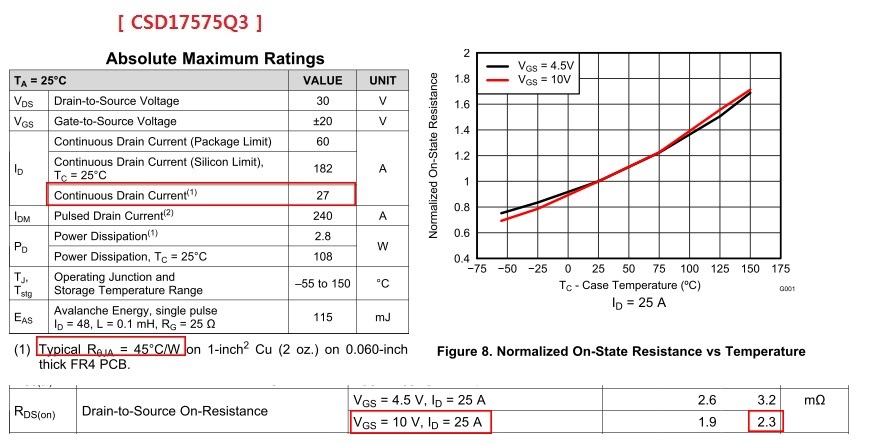

for CSD17575Q3,

Continuous Drain Current is defined 27 A at RӨJA = 45 ⁰C/W and Ta = 25 ⁰C.

I want to estimate the allowable Continuous Drain Current at Ta = 100 ⁰C with RӨJA = 45 ⁰C/W and Vgs = 10V/Id = 25A conditions.

Max Rdson at Ta = 100⁰C would be 3.91 mohm(= 2.3 mohm x 1.7).

the allowable Continuous Drain Current at Ta = 100 ⁰C would be 16.73 A [= root(( Tjmax - Ta )/(RӨJA x Rdson)) = root(( 150 ⁰C - 100 ⁰C)/(45 x 3.91 mohm))]

my calculation above is correct ?