Other Parts Discussed in Thread: SN6505B

Hi,

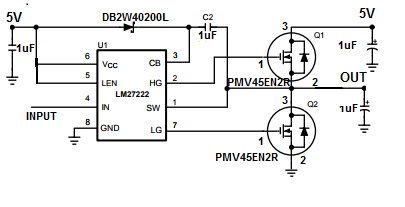

We am trying to use LM27222 as a standard push pull driver, driving two N-Ch FETs into a load of 2A. The input to PWM pin is either DC or pulsed - when pulsed, its a frequency of ~ 100Hz with high period of ~100usec. The output switching needs to be fast, changing within 100nsec of the PWM input rise/fall edges. The VCC as well as PWM input levels are 5V. The high side mosfet Vin is also 5V.

My queries are:

1) Can the device handle this kind of a switching, as the datasheet mainly intends to show this only in a buck regulator configuration.

2) We will chose a low Rdson mosfet (~40mOhm) to minimize drop over the high mosfet and have almost 5V appear at the output. Is that ok?

3) There shall be no L/C configuration at the switching node SW. The output shall directly be fed to the load. Is that ok?

Regards

Gaurav