Hi,

I have some additional questions about the TPS3700-Q1:

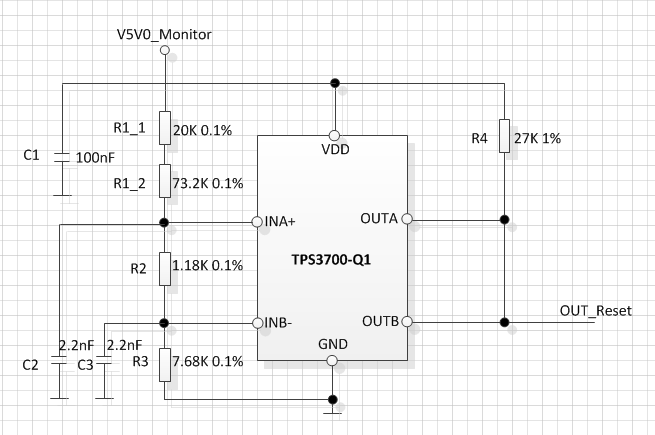

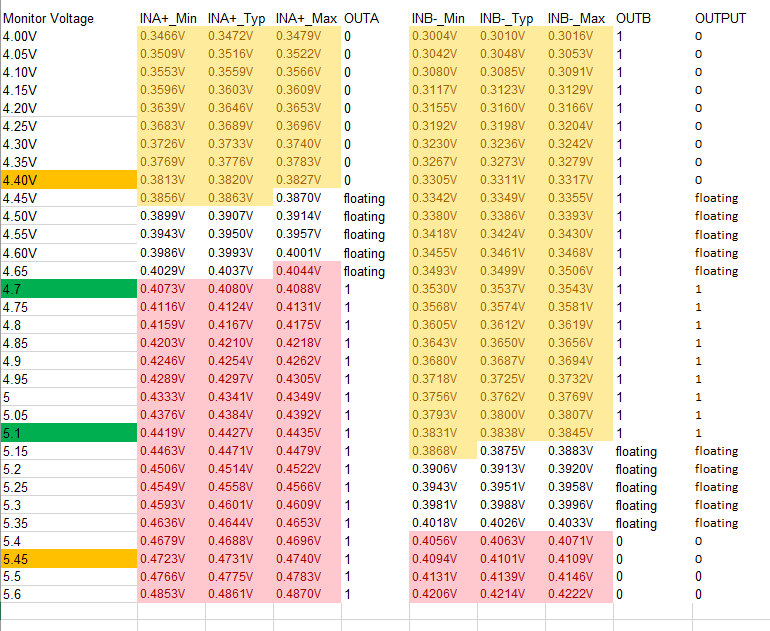

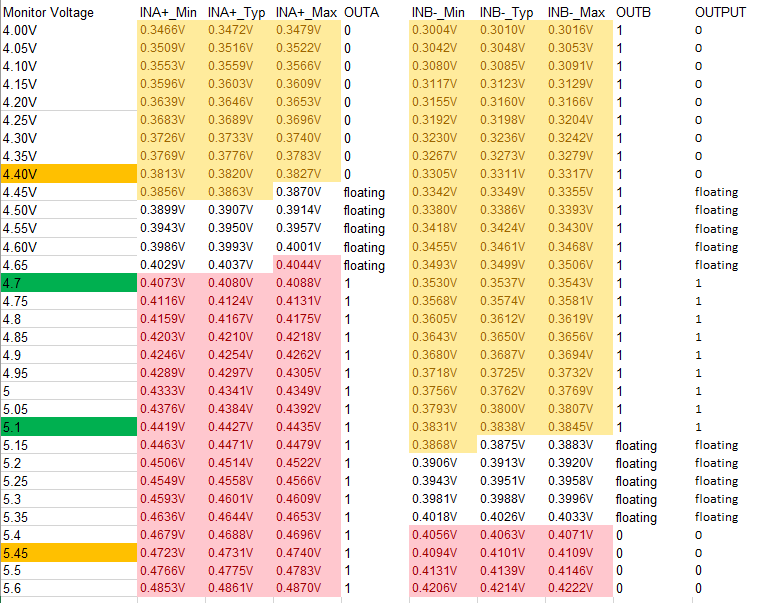

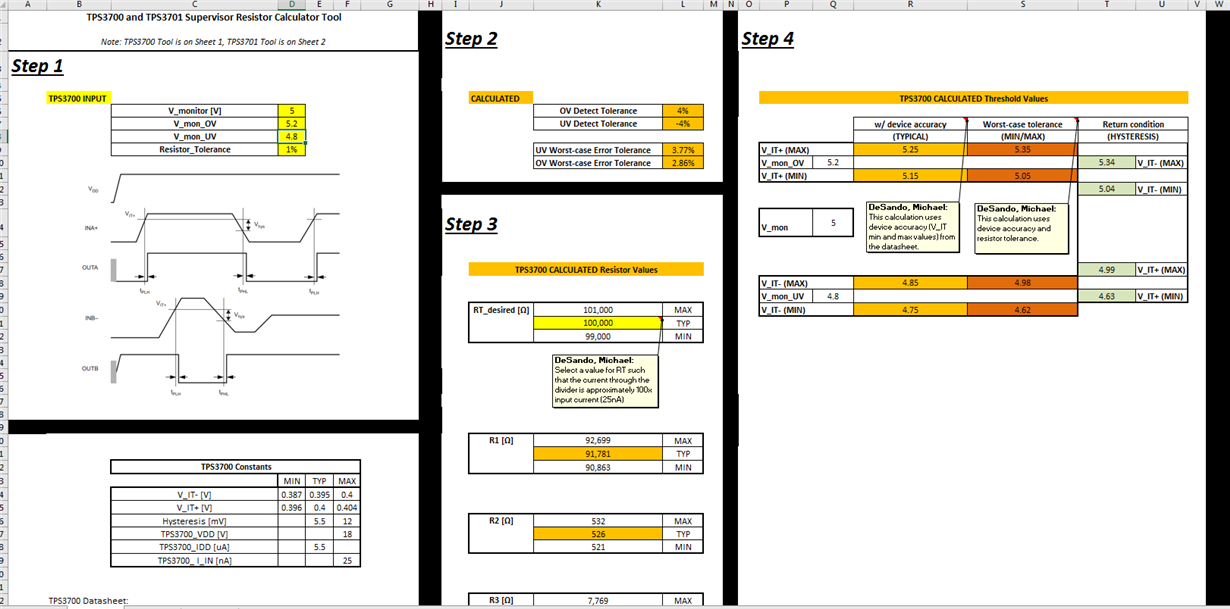

1.How to choose an suitable value for RT?

According to my calculation like:

Assumption: V(Monitor)=5V

I(INA+ + INB-)=25+15=40n A

RT≈V(Monitor)/100* I(INA+ + INB-)=5/100*40=1.25Mohm

I am not sure if my calculation is right for RT ?

Consider our product is not recommended for use the resistor higher than 100Kohm, so my question is if we can choose the more higher current than the input current at the INA+ and INB- terminals?……

For example, 1500- times , thus RT≈V(Monitor)/1500* I(INA+ + INB-)=5/1500*40=83Kohm….Is it ok ? or Will it bring the bad influence to device?

2.There has two equations for R2’s calculation, thus we will figure out two value…How to choose the value?

3.How to calculate the pull up resistor on the output line?

My understanding: Rpu=(Vpu-VLV) /IS (Vpu: Pull up voltage ;VLV: Output voltage low ;IS: Output sink current)

Is it right?

4.If it necessary to reserve the bypass capacitor on Input line(INA+, INB-)?

Thanks!!!