Customer is evaluating LMG3410-HB-EVM (and LMG3410-BB-EVM), but L2(inductor) was increased over 120℃ by thermograph.

User's guide is described that heatsink and airflow are recommended, but I think these idea is not critical for decrease L2 temperature.

(L2 was not decrease temperature)

Please let me know about two points question below;

①Is there proposed measures by L2 temperature?

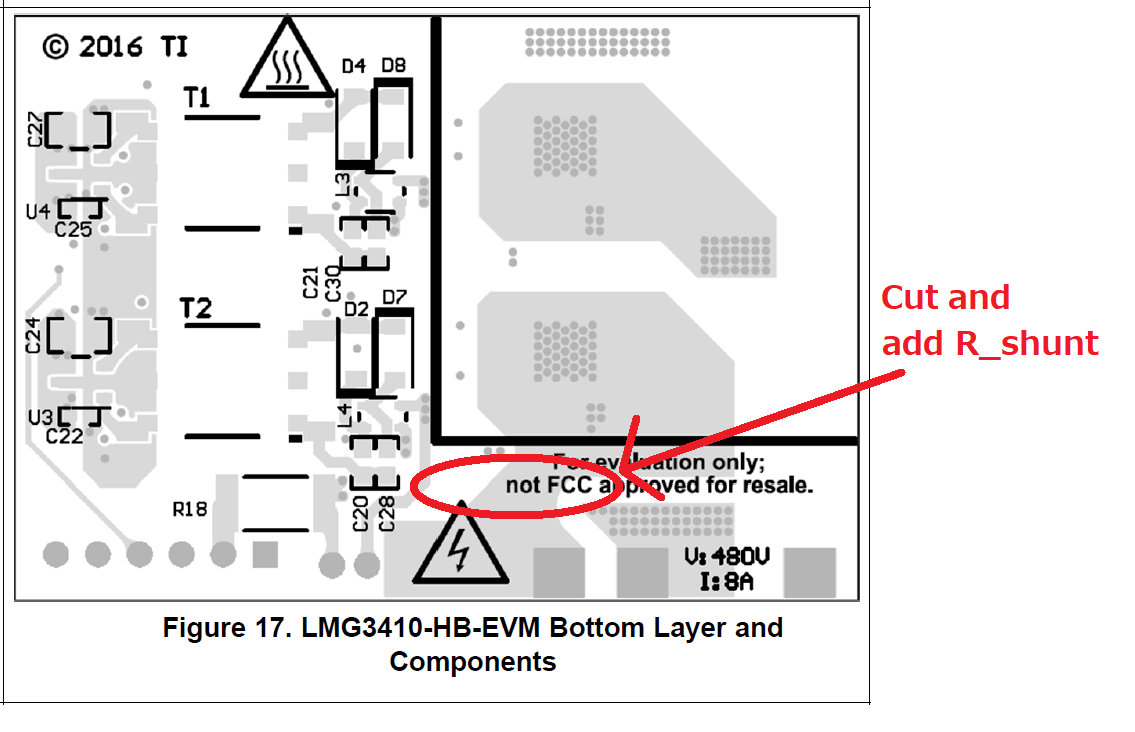

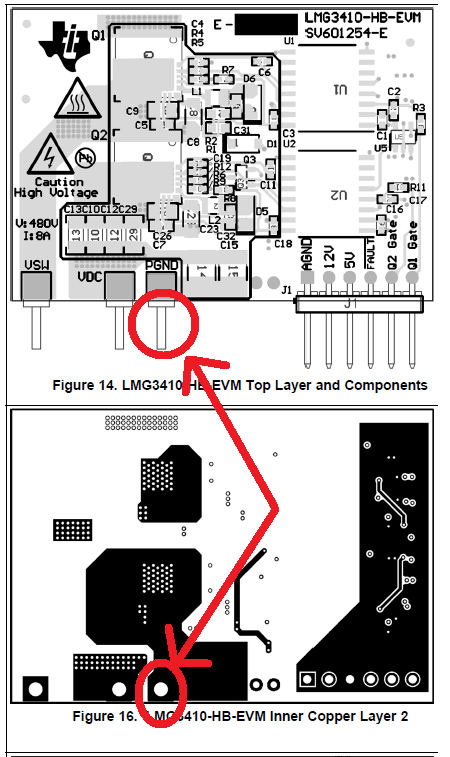

②Please let me know about measuring method for High-side GaN's drain current.

【Condition】

・Input(Primary): DC 400V

・Output(Secondary): 200V

・PWM: 5Vpp

ON Duty:0.3~0.5

・Pout: 35W(ON Duty:0.3)~100W(ON Duty:0.5)

・fsw: 50kHz

・Ta: about 20℃

Best regards,

Satoshi