Other Parts Discussed in Thread: UCD3138

Hello

I tested your company's UCD3138 full-bridge hard-switch development board and designed a 200W switching power supply prototype based on your development board.

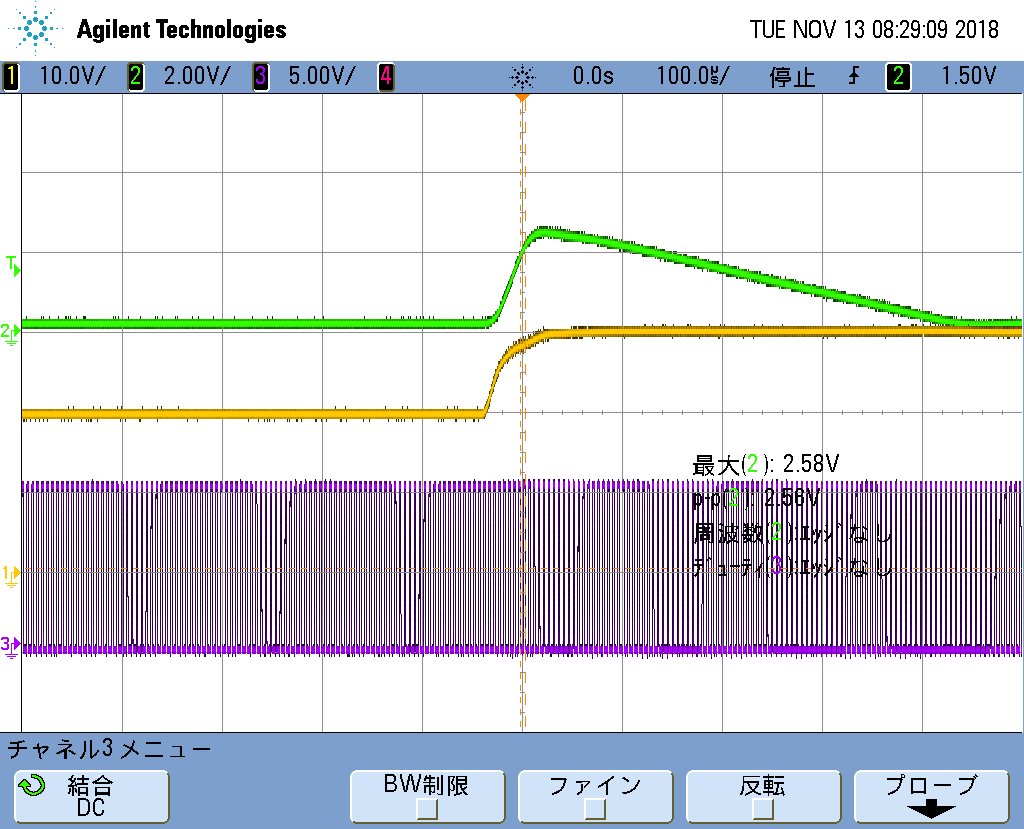

I tested the input step waveforms of your development board and our prototype. The figure below is the input step waveform of our prototype.

As shown in the figure above, when the input voltage jumps from 20V to 30V, the output voltage jumps up to 2.5V and the recovery time is nearly 500us.

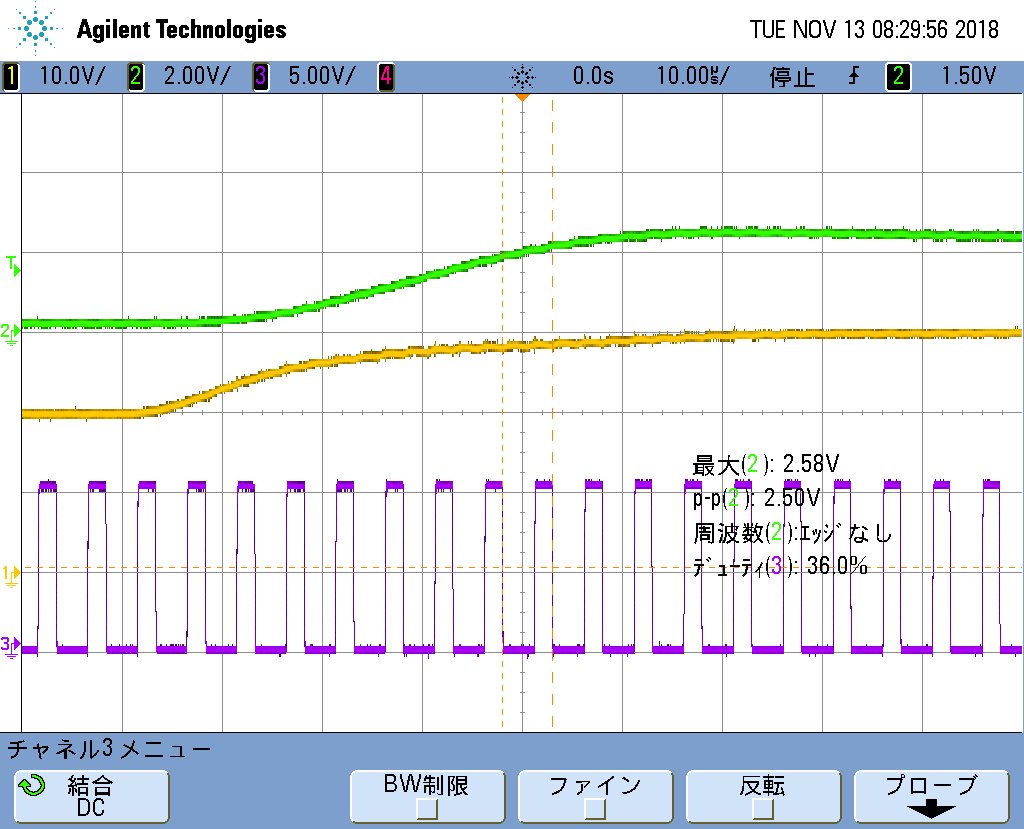

The figure below changes the timeline and expands the waveform.

It is found that the duty cycle D of the UCD3138 remains constant for 50us of the input voltage transition and does not decrease as the input voltage increases.

After 50us, the duty cycle D gradually decreases, and the output voltage gradually returns to the target value.

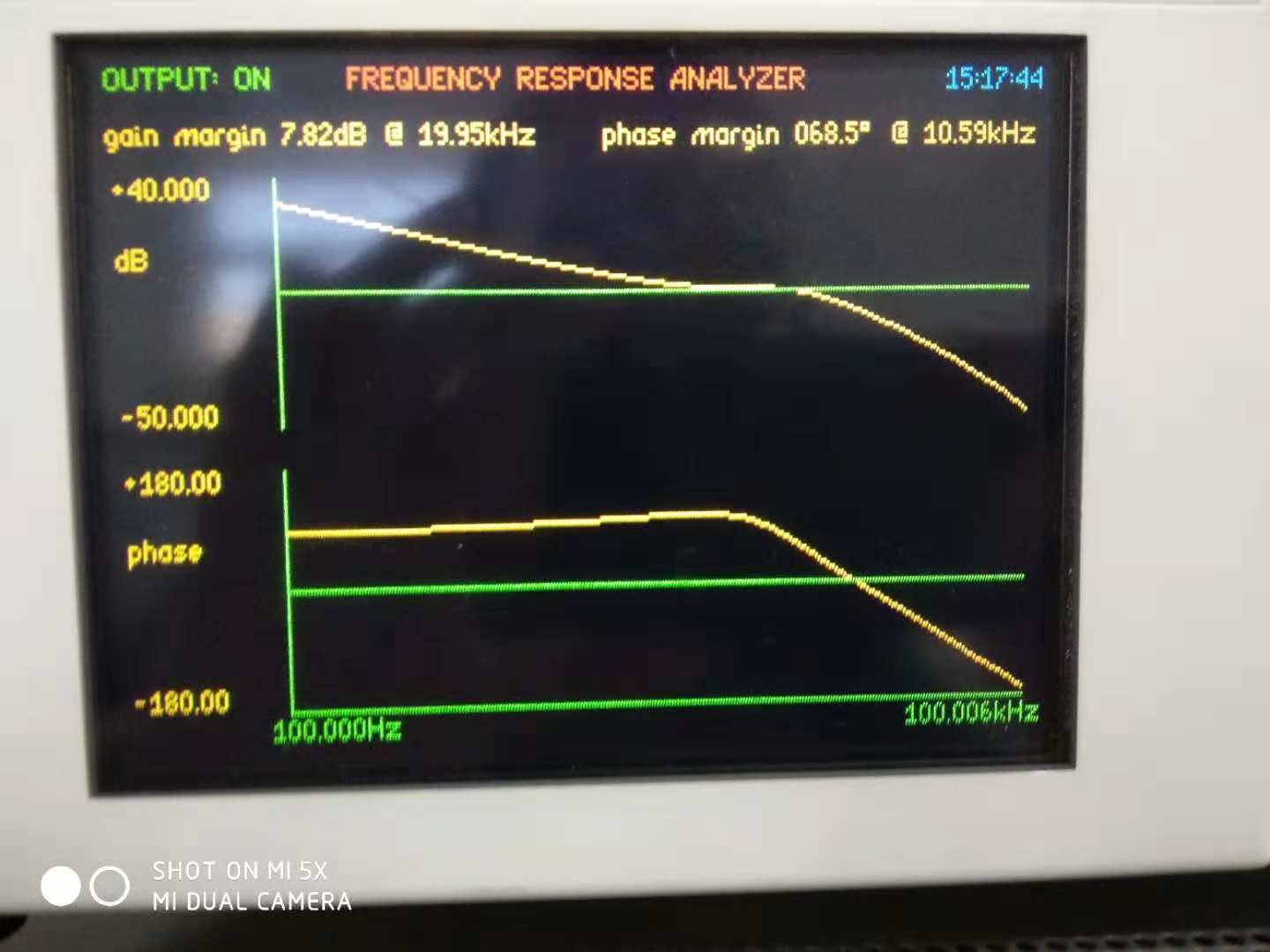

I tested your development board again, with a load jump of about 500mV and a shorter recovery time.

I am very confused about this.

The switching frequency of the prototype is 200 kHz, which is the duty cycle updated every 5 us. The prototype only uses output voltage feedback control and does not incorporate feed forward control of the input voltage.

I suspect that your development board should enable the input voltage feedforward function, so the response to the input voltage will be much faster.

However, I am still very confused.

Although I did not enable the input voltage feed forward and only used the output voltage feedback control, why does the feedback adjustment take place after the input transition delay is 50us ?

The switching period of my prototype is 5us, that is, there are 10 cycles of delay.

The manual introduces the PID link of UCD3138 as an analog circuit. After the initial configuration is completed, it can be run independently.

Why is the PID link that only enables output voltage feedback control delayed by 50us? Instead of real-time control, that is, after a switching cycle of 5us, start to adjust?

UCD3138 For the adjustment of the input step, is it necessary to enable the voltage feed forward function, otherwise it can not be quickly controlled?

Thank you

ZJYL