Hi,

This is Sanjay

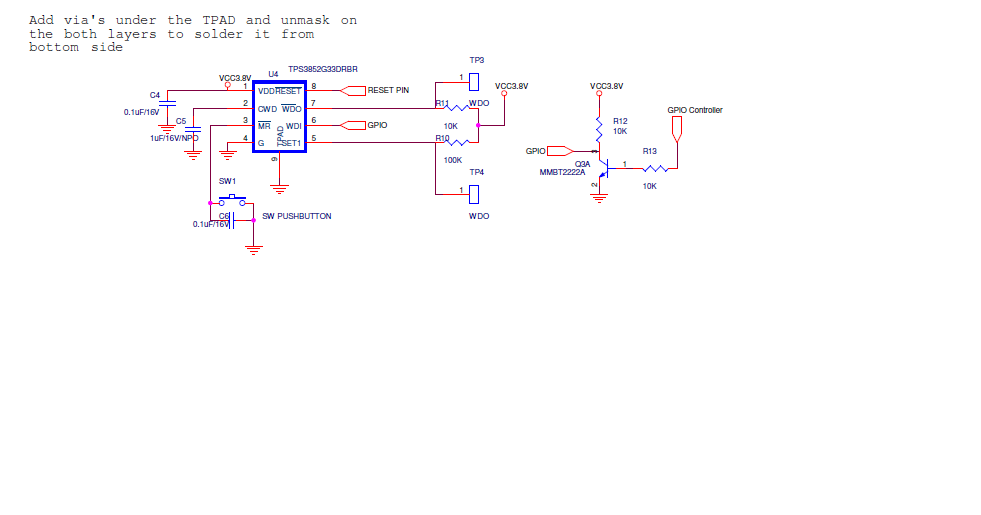

I have developed a watchdog circuit using TPS3852G33DRBR on a General purpose Board and found not functioning. I have stopped the WDI pulse by making it continuous High or Low to get the RESET out. But, it is not generating any RESET pulse. But, Manual Reset is functioning. Please do suggest for any modificationsTPS3852G33DRBR Schematic.pdf