Other Parts Discussed in Thread: TPS65261

Tool/software: WEBENCH® Design Tools

Hi team.

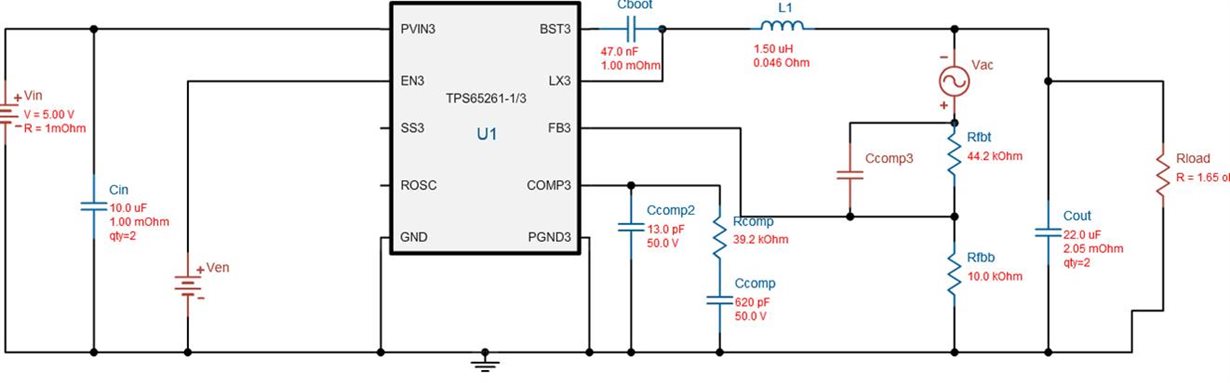

I did simulation for TPS65261-1 via WEBENCH.

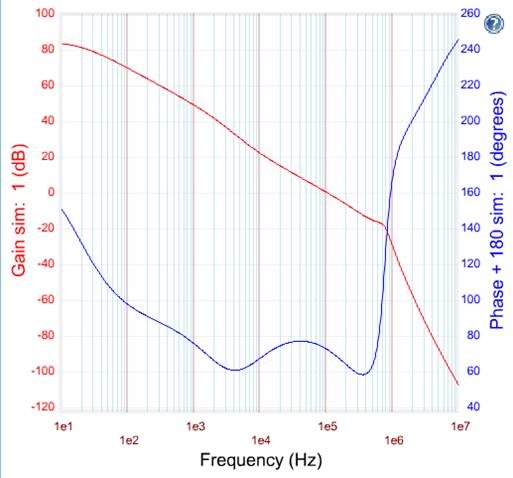

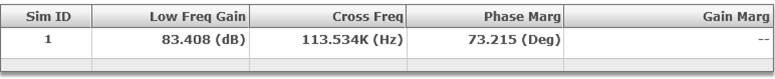

However, the bode plot result of Vout3 was output in a different form than normal.

It is normal?

If it is no, how does this affect the system?

Please analyze this result.

The above is the result when 1.5uH is applied to Lout.

Even when applying 2.2uH to Lout, similar results are obtained.

Result data(1.5uH) : TPS65261-1_1.5MHz_1.5uF.pptx

Result data(2.2uH) : 6428.TPS65261-1_1.5MHz_2.2uF.pdf