Other Parts Discussed in Thread: TPS2595,

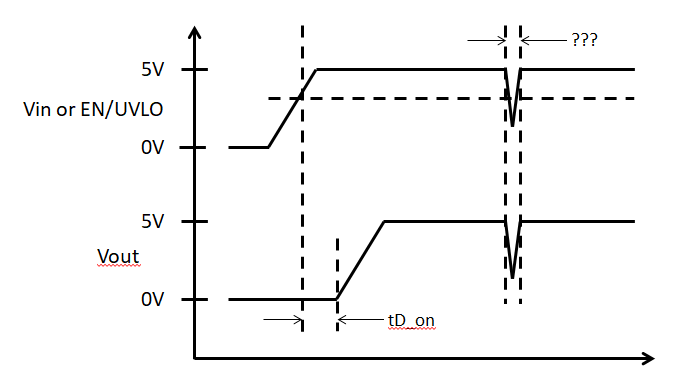

Please let me know about UVLO response time for instantaneous power failure.

I want to know the condition of power failure and momentary recovery.

When the time for power failure to recovery is too fast, I guess that UVLO can't detect this failure.

Is there spec for require failure time?

Best regards,

Satoshi