Other Parts Discussed in Thread: TINA-TI, , LM5145, INA169, LM5117

Tool/software: TINA-TI or Spice Models

Hi,

Whilst busy inside simulations using LM5085 I noticed that I was seeing significantly higher switching losses from the power FET and investigated. I have generated a few questions.

Q1. The Datasheet for the LM5085 states that the gate drive is capable of ~1.5A and has an output Resistace of 2.3ohm (@500mA). However I noticed that the Spice model shows gate currents of only 150mA. I tested this both whilst driving the FET and to be sure I strapped the gate output to Vin through a very small resistor to see what current the gate pin would sink when the converter attempted to start. ~154mA. This is much much lower than expected. Can anyone explain?

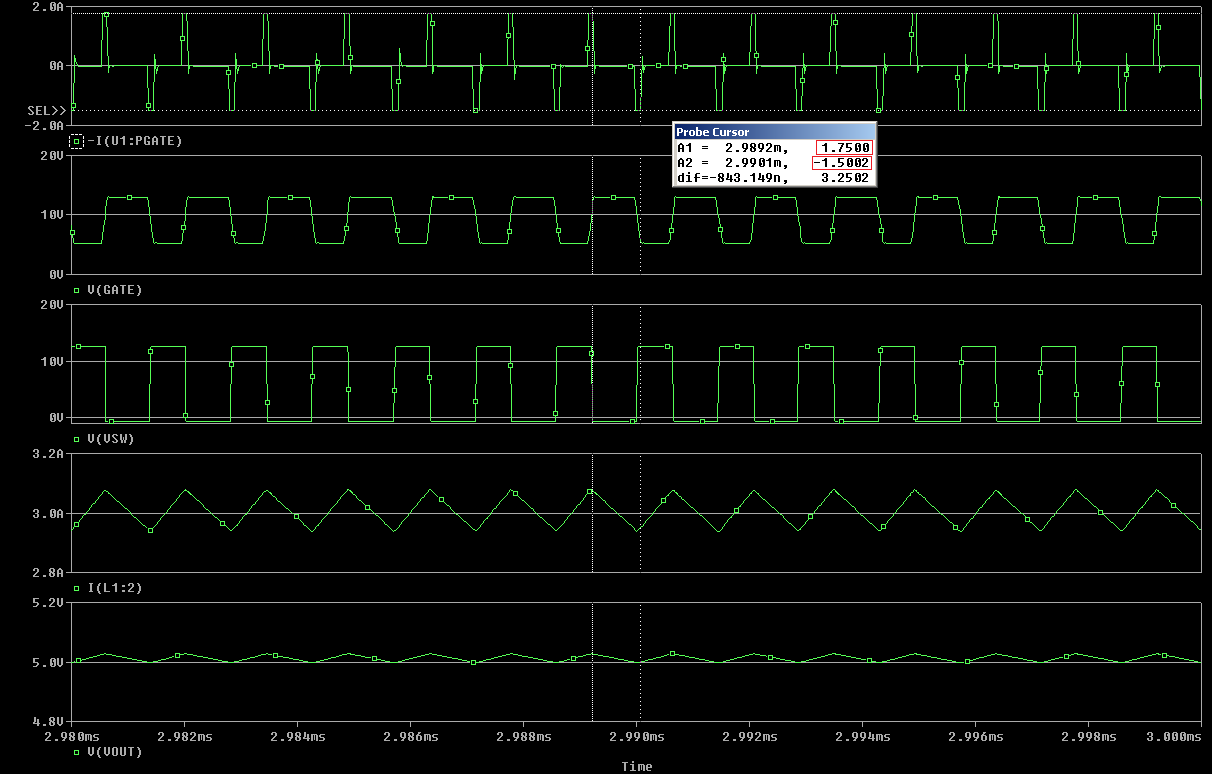

In an attempt to see how that converter would perform with more reasonable gate currents, I followed the gate output with a BJT push pull pair between Vin and Vcc, using some high speed BJTs, the affect was dramatic. The gate drive current on the active side of the PP pair jumped as expected to >1.5A peak. Switching times significantly improved and the efficiency jumped up 'a lot'.

The lower leg of the PP pair was connected to Vcc, therefore this 1.5A was being sunk into the Vcc pin.

Q2. Would the real IC actually allow such currents to be sunk into the Vcc pin? The datasheet states Vcc Current limit at 40mA, but it does not state sink or source. I strongly assume this configuration would be invalid.

In the process of doing this I noted that the datasheet states, "The regulator is disabled when the LM5085 is shutdown using the RT pin". When I shutdown the model in this way the Vcc pin stays nailed at Vin-8V.

Q3. I assume that with the real IC, when in shutdown, Vcc would float up to Vin rapidly. Can you confirm this?

Finally can you comment on the idea of following the gate output with a higher power driver. like I described. I'm hoping that this is just not necessary, but the drive I'm getting from the Spice model is just not enough.

I am designing a 60V in....42-60V current regulated converter, capable of 8A output at any voltage between 42-60V. That's around 400W as a system. Looking at the datasheet it is almost impossible to predict efficiency, but using simulations I am surprised at the results. I have designed the converter to run at around 60Khz, in an attempt to reduce switching losses, which as expected predominate. Even so, with the LM5085 as the sole gate driver I am seeing between 10-20W power dissipation in the PFET, depending on the particular FET I use. When I drive the gate with an auxiliary driver I can reduce this power loss to < 3W. This makes a huge difference to the package type and heat-sink requirements of the PFET.

This is an awful lot of simulation and not much reality, but I would appreciate any feedback on my questions and comments on the application.

Many thanks

Aidan