Other Parts Discussed in Thread: TIDA-00449

Hi,

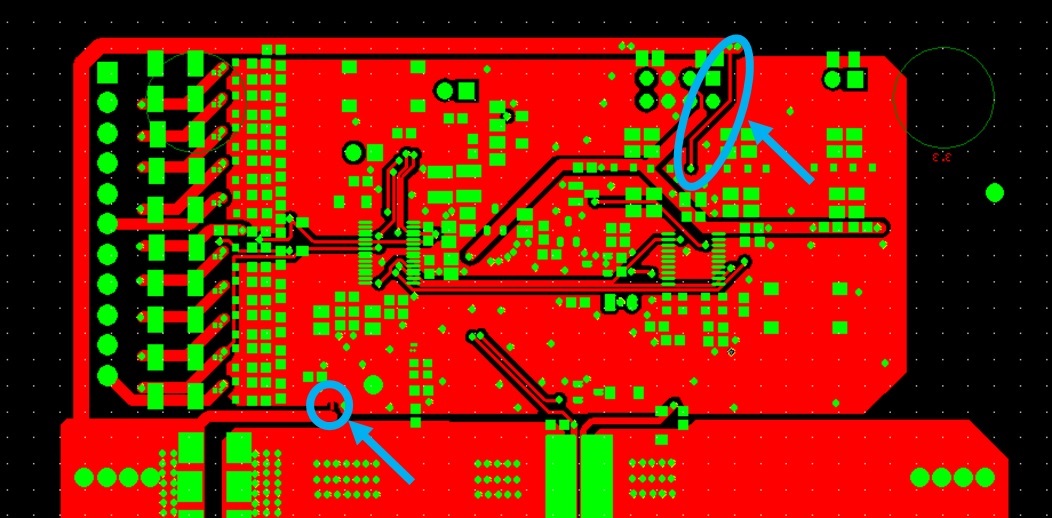

Could you take a look our schematic & kindly advise about the below questions please?

1. ZD10 : Could we add a zener diode (36V) on the track between VC10X & VC5X?

2. ZD11 : Could we add a zener diode (36V) on the track between VC10 & VC5X?

3. ZD12 : Could we add a zener diode (36V) on the track between VC5 & VSS?

*For above ZD10, ZD11 & ZD12, I am going to use MMSZ5258B (https://www.diodes.com/assets/Datasheets/ds18010.pdf)

4. C59 & C60 : Could we add these 2 capacitors (0.1uF 50V) as a serial connection on the track between VSS & VC10?