Other Parts Discussed in Thread: UCC2895

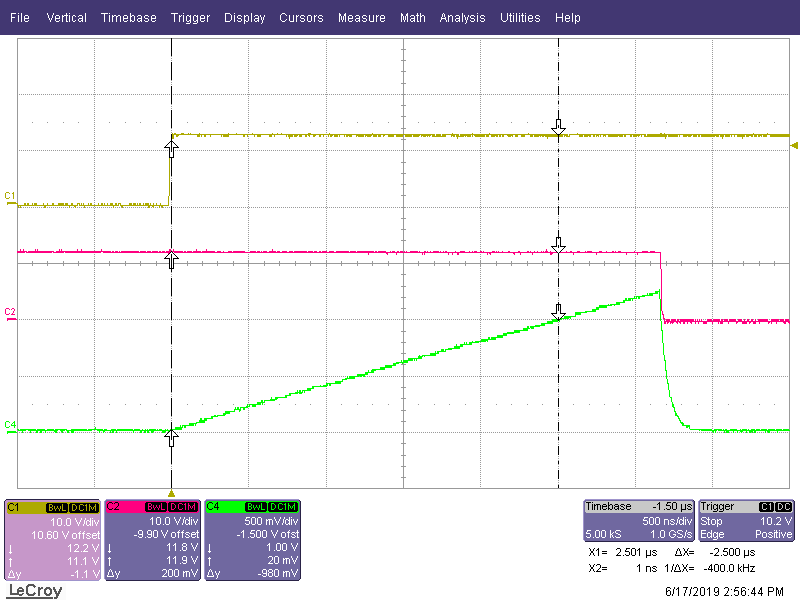

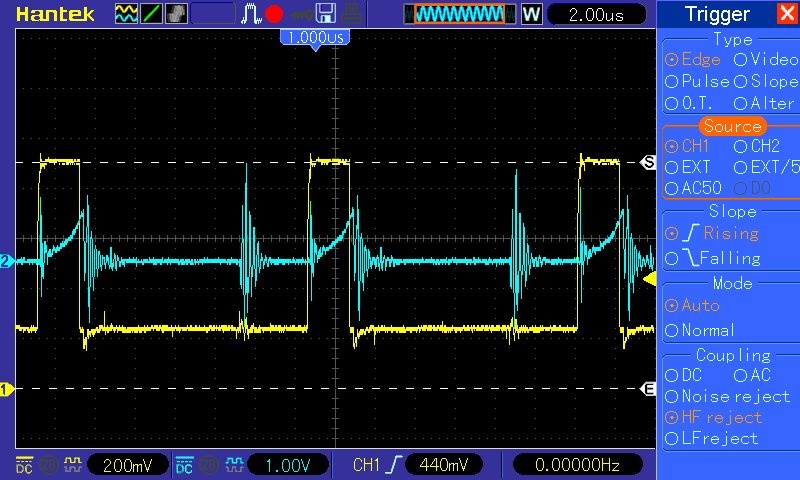

In my phase shift full bridge converter design I have designed in an RC filter on the current sense input to the chip as recommended in numerous app notes etc, but I am seeing a volt-drop across this filter when I connect it to the current sense input to the chip, as if the chip is loading the circuit. In fact, based on the volt-drop, I would estimate the effective input impedance of the chip to be around 1k ohm. What is more, this impedance seems to be switched as the peak current point is approached, as if a sample and hold is being switched in, which pretty much shorts my current sense signal out altogether, just at that moment.

There is no mention of this kind of behaviour in any literature, so I assumed by lack of any special detail that the input impedance of the pin should be very high. I've seen this with two chips, so I don't think it is to do with chip damage, but I can't rule it out.

Has anyone seen this behaviour before? Is it the expected behaviour?