Other Parts Discussed in Thread: UCC21732QDWEVM-025, UCC21750, UCC21732,

Hi,

I am implementing a boost converter using Cree C3M FETs with a split source connection and 2 UCC21710-Q1s for high and low side drive. I am trying to figure out how to implement the overcurrent protection utilizing the OC pin and a sense resistor I am a little confused on how to connect the source sense pin and source of the FET. Based on Figure 15 on page 23 of the datasheet it shows a sense resistor (which i have calculated to be 175 ohms to set OC limit to 200A) connected between kelvin source and power source. Then it shows power source going to COM. However, everywhere else in the datasheet recommends connecting the kelvin source to COM on the chip and this makes sense as to keep the gate and power loops as separate as possible. Does using the OC pin prohibit use of the kelvin source on the FET as the COM connection to the chip? Figure 18 shows the same setup but does not explicitly show the connection to COM on the chip (just has a gnd symbol named COM). Would it not be best to place the sense resistor across kelvin source and source, but still bring kelvin source to the COM?

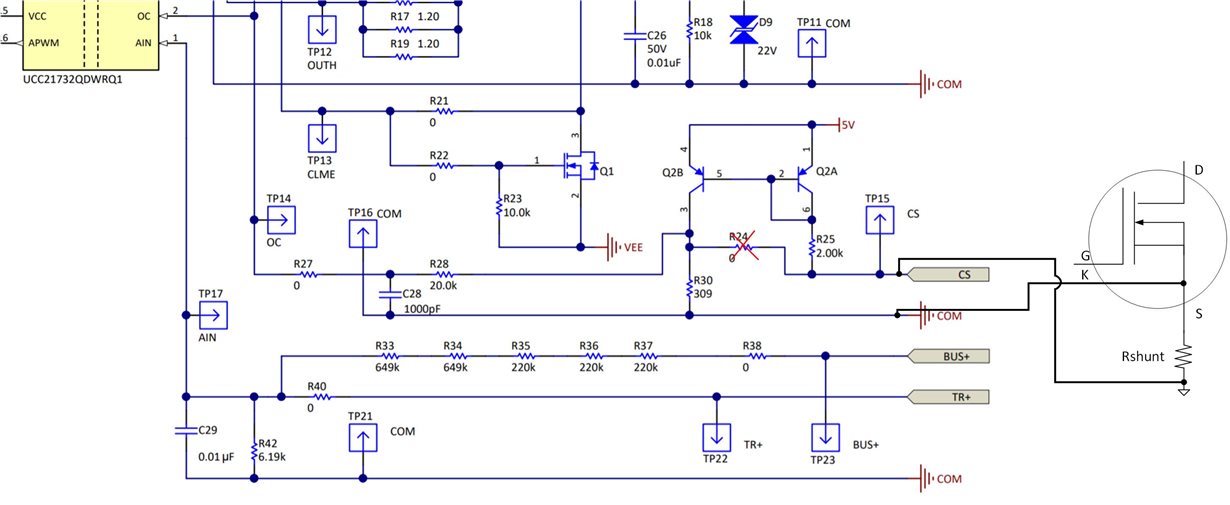

I've looked at a few eval boards with similar gate drivers such as CC21732QDWEVM-025, but it only seems to confuse the application more. For positive OC sensing it shows just a series connection to a 20k (which is a type in the document, the BOM pn shows 2k) and then a filter cap. For negative OC sensing it shows a 309 ohm shunt resistor across kelvin and COM which i assume is power source on the FET. This is confusing since these differences are not explicitly covered in the respective data sheets. Any guidance on these design challenges would be appreciated.

-Tim