Other Parts Discussed in Thread: UCD90SEQ64EVM-650, UCD90160A

Q1: Why OFF sequence with warm?

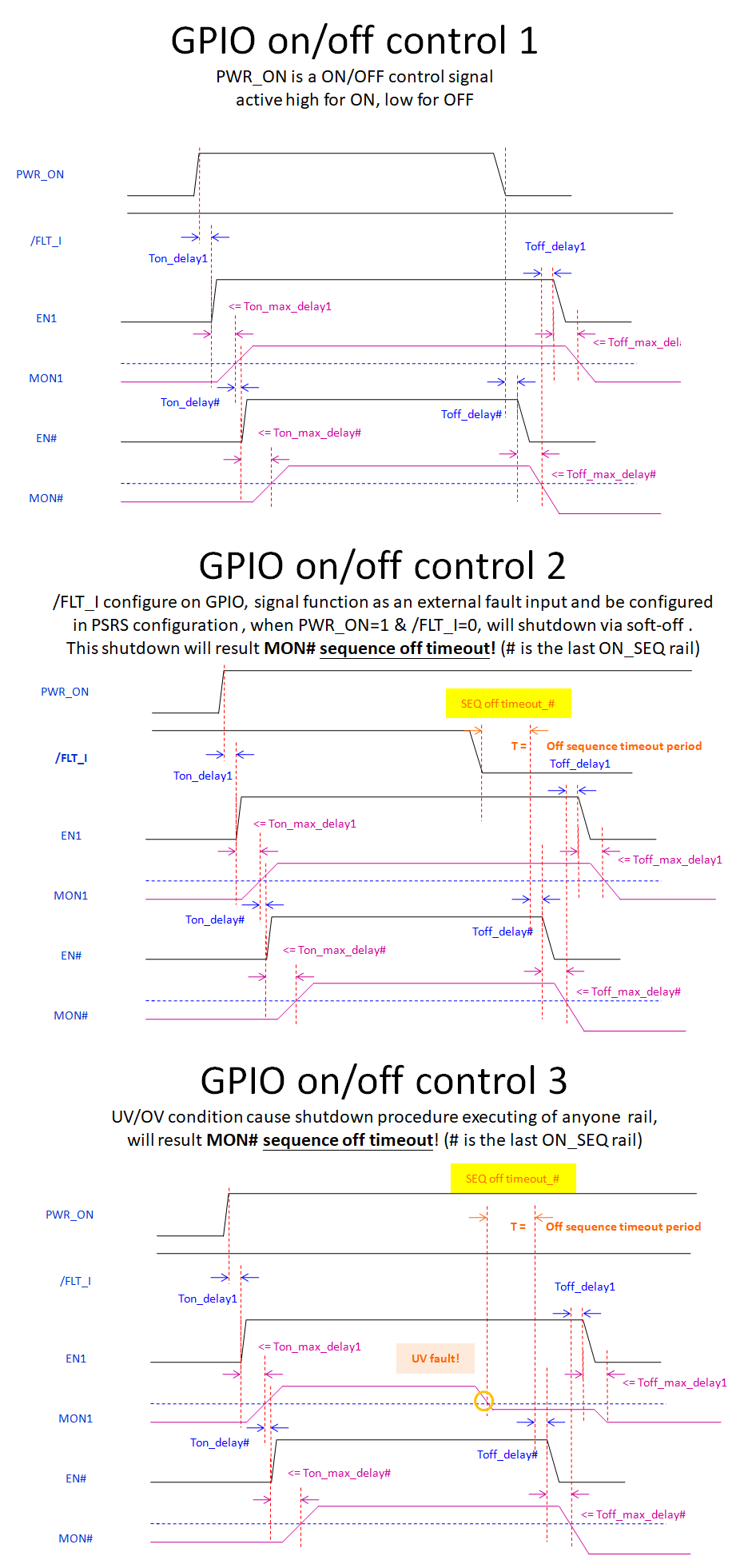

I have configured 2 GPIO to control 10 rails power, one is "PWR_ON" ,active high for power on/off control, other is "/FLT_I", active low, it's function as external fault signal input to disable "PWR_ON" turn-on & shut down all rails when "/FLT_I" = 0; 3 type behavior be described following:

1."PWR_ON" behavior is correctly !

"PWR_ON" = 1 (with "/FLT_I"=1), all rails turn on following the on-sequence.

"PWR_ON" = 0 (with "/FLT_I"=1) all rails turn off following the off-sequence.

2."/FLT_I" behavior result a warm message:<off sequence timeout> on rail #9 & rail #10 with correct off sequence.

I make sure the time is equal to rail #10's off sequence timeout period (time between "/FLT_I" falling to low and rail #10's enable de-asserted to low ).

3. UV/OV of any rail fault (except rail #10) cause shut down behavior result a warm message:<off sequence timeout> on rail #9 & rail #10 with correct off sequence.

I make sure the time is equal to rail #10's off sequence timeout period (time between "MON #" voltage below the power good off and rail #10's enable de-asserted to low ).

I expect the shut down procedure is a correct off sequence without any warm , but type 2 & 3 still get off sequence timeout !

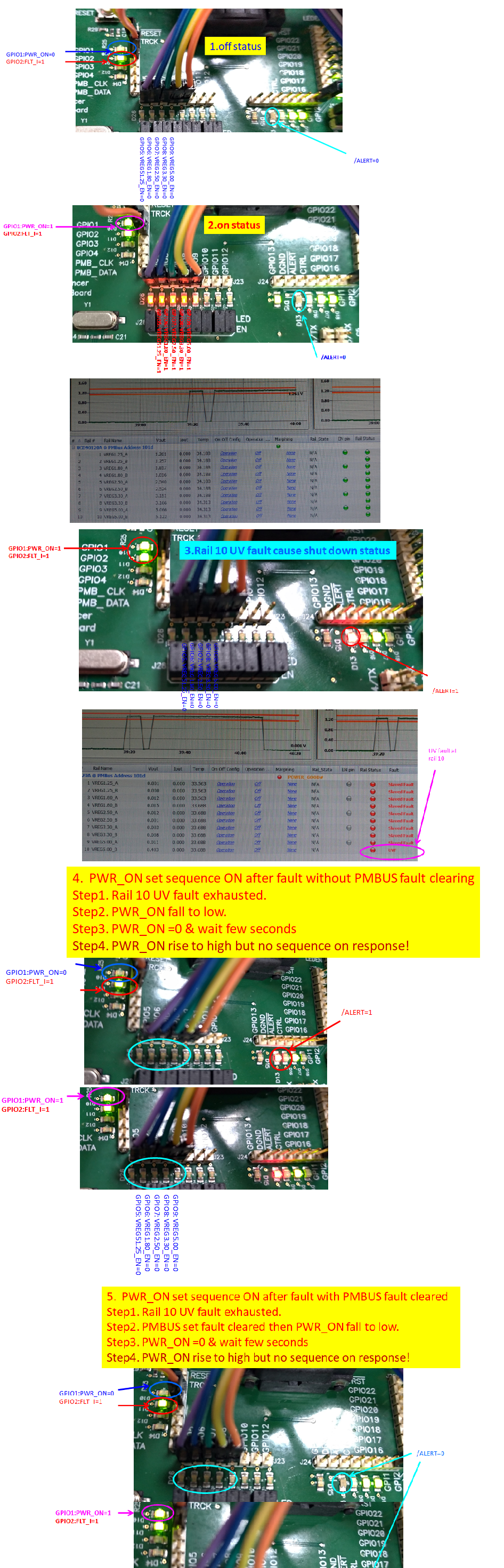

Q2: How to execute ON sequence again after shut down via any fault?

My UCD90120A will shut down following off sequence when any fault occurred, I clear all faults via the PMBUS then drive "PWR_ON" from 0 to 1 , but the on-sequence cannot produce again!

Only press /RESET button on the EVB of UCD90SEQ64EVM-650 to reset chip, the "PWR_ON" signal can be available again!

Is the rs-start configuration problem ? How do I configure the re-start can match above function description?

May anyone can give me any advice to solve it ? Thanks a lot!

My UCD90120A configuration setting file: