Hi,

we met some problems with TPS548D22, attached is the design schematics of our application, could you please help to check below items?

1, help to review the schematic, to double confirm if there is any design weakness

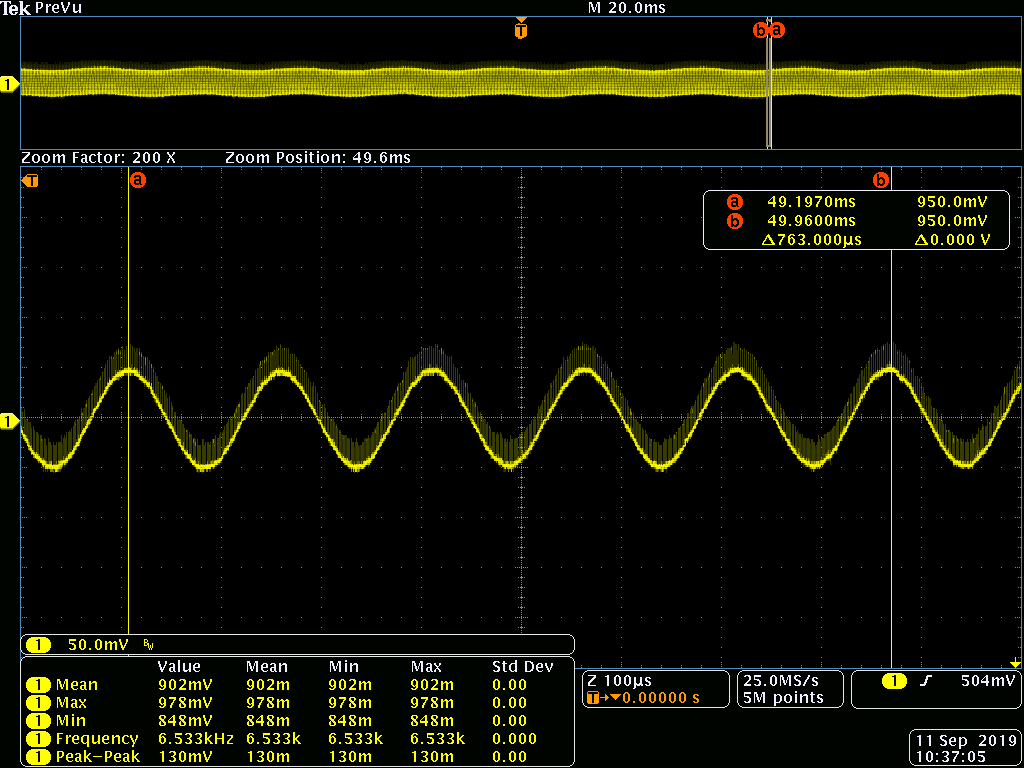

2, usually our output inductor has 2-3 sources, with one of them, there sometimes will be low frequency oscillation on the output voltage, you can find waveform through the attachment, do you believe this is caused by insufficient ramp compensation? As the failure will disappear if we tune the ramp compensation from R/2 to R. AND can I know how much inductance tolerance can our VR design tolerate, is there a way to calculate it?

3, sometimes it only appears at high temp. but there will be similar oscillation at power up when in normal temp, can you help to explain how this will happen? Or what parameters may impact this? Output inductance or other components?

4. seems when inductance is becoming large, the low frequency oscillation will occur easily, and tuning the compensation to R will address it. So my question is if there is paper calculation to verify if increasing inductance to 1.2uH will induce such kind of instability? Thanks.