Other Parts Discussed in Thread: TPS51120,

Hi team,

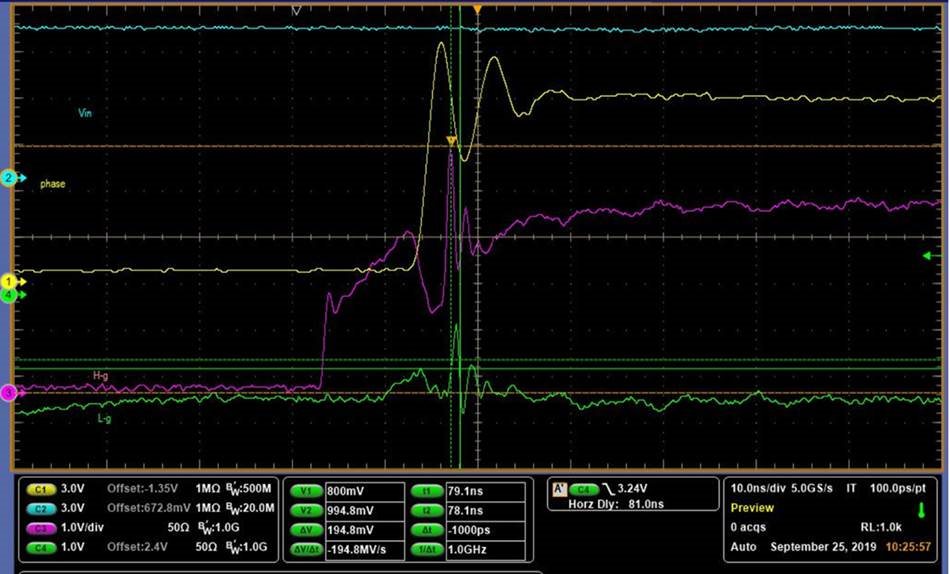

Our customer is using CSD87350Q5D with TPS51120, and when they add a 11A load to the output, there will be a surge at both H/L Vgs, which may cause the H/L FET turning on simultaneously, the surge duration is about 1ns, please refer to the waveform below.

According to the datasheet, the turn on delay time of CSD87350Q5D is 7ns(Q1) and 8ns(Q2), but both is type value, do we have the minimum value? Will the 1ns surge cause both H/L FET on and bring damage to the circuit? Could you please give some comments on that?

Thanks.

Best Regards,

Livia Liu