Hi,

We've ran into issue with switching supply from Cell Pack to Adapter+ .

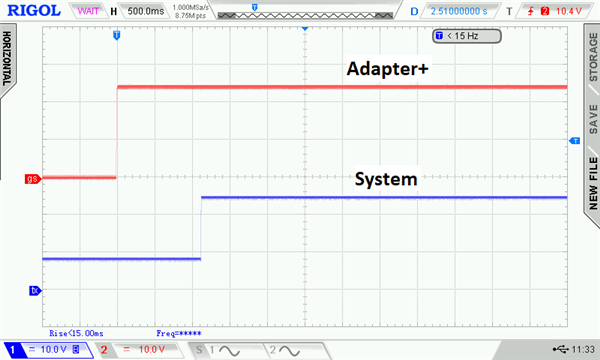

Initial Setup: "System" is supplied by "Pack+". At some moment "Adapter+" is connected.

Problem description: There is significant delay (~1.1s) between the moment when voltage to "Adapter+" node is applied and moment, when we see voltage increase on "System" node. (all names for nodes are taken from datasheet, for naming compatibility)

After research of problem, we noticed, that same delay exists on ACDRV pin.

According to datasheet, : ACDRV is "Charge pump output to drive both adapter input n-channel MOSFET (ACFET) and reverse blocking n-channel MOSFET (RBFET). ACDRV voltage is 6V above CMSRC when voltage on ACDET pin is between 2.4V to 3.15V, voltage on VCC pin is above UVLO and voltage on VCC pin is 275mV above voltage on SRN pin so that ACFET and RBFET can be turned on to power the system by AC adapter. Place a 4kΩ resistor from ACDRV to the gate of ACFET and RBFET limits the in-rush current on ACDRV pin.

Our measurements show that before/after (after = some micro- or milliseconds later) "Adapter+" is applied, Voltages are following :

1) Voltage on ACDET is 1.2 / 3.0V (1.2V is due to circuit, discussed in e2e.ti.com/.../561130 , which is required, to retain I2C communication, even when there is no "Adapter+ voltage applied"

2) VCC is equal or higher than Pack+ voltage

3) SRN is equal to Pack+

Interesting observation: when the circuit is launched the most first time (i.e. first - cell pack is attached, and then - adapter+), the delay is around 150ms ; later, if we turn off adapter+ and the turn it on again, all next attempts give 1.1seconds delay.

What could be the reason of this delay, and how can we eliminate it?

P.S.> If schematics is required, please let us know - I'll e-mail it.