Dear Sir,

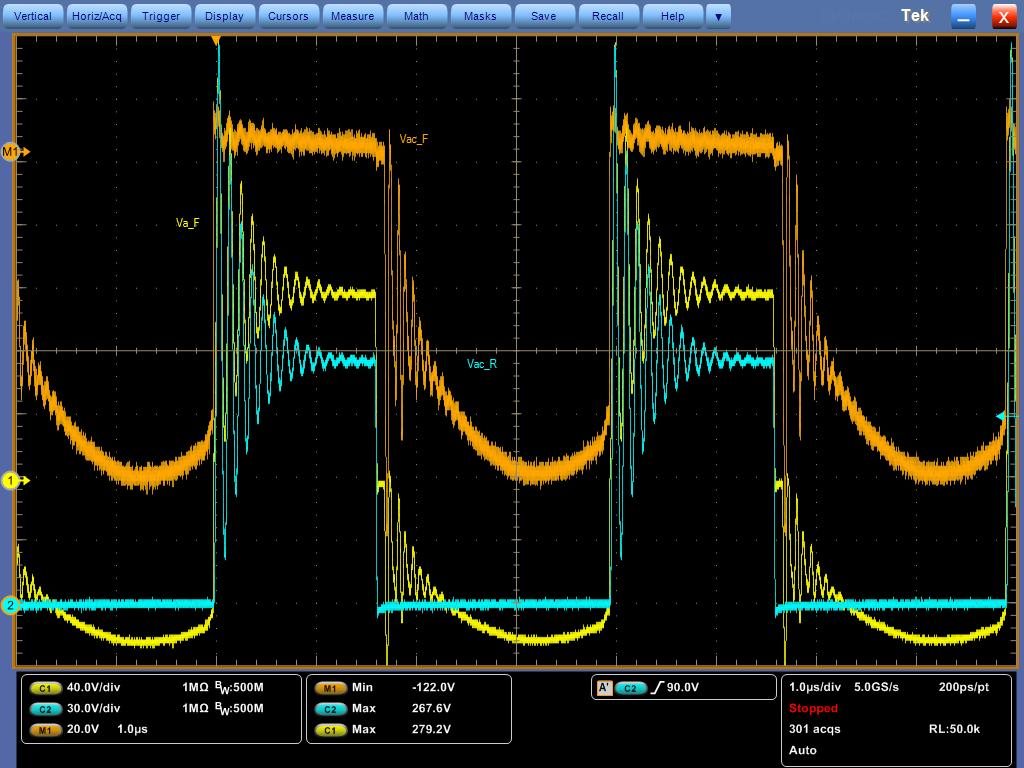

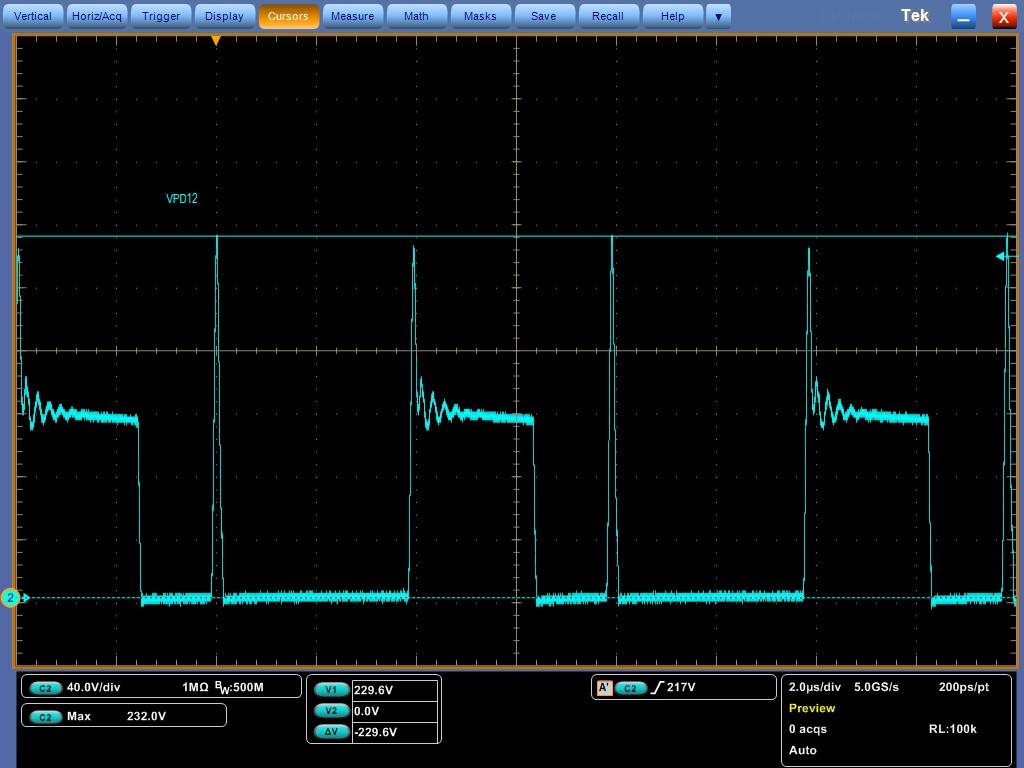

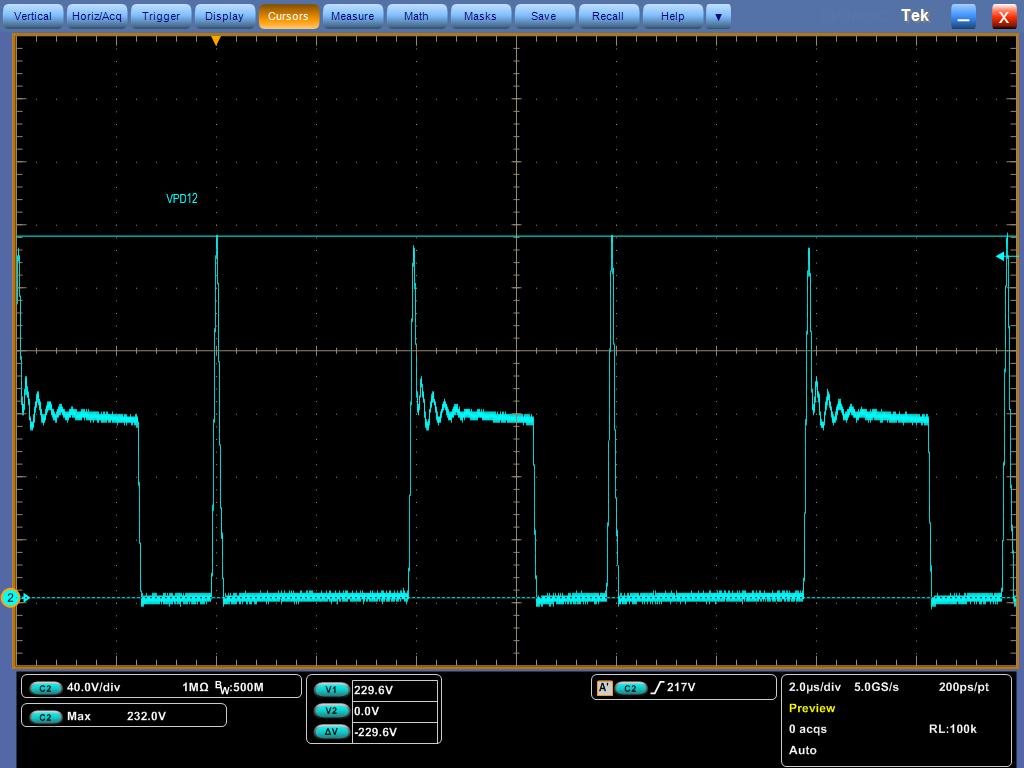

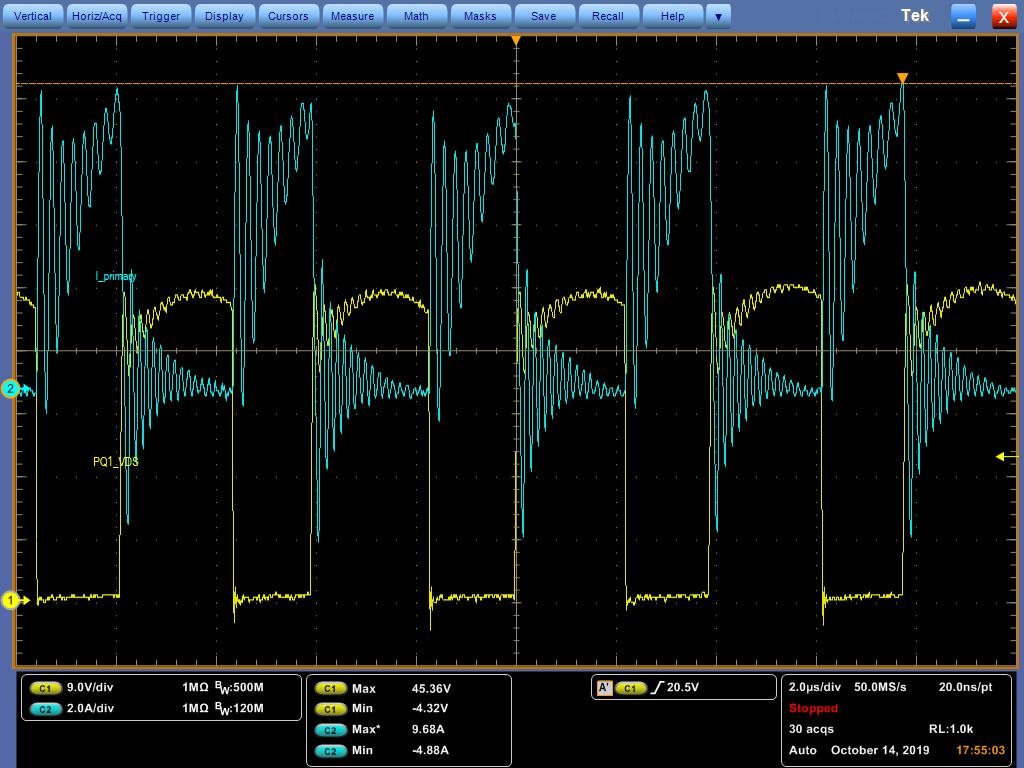

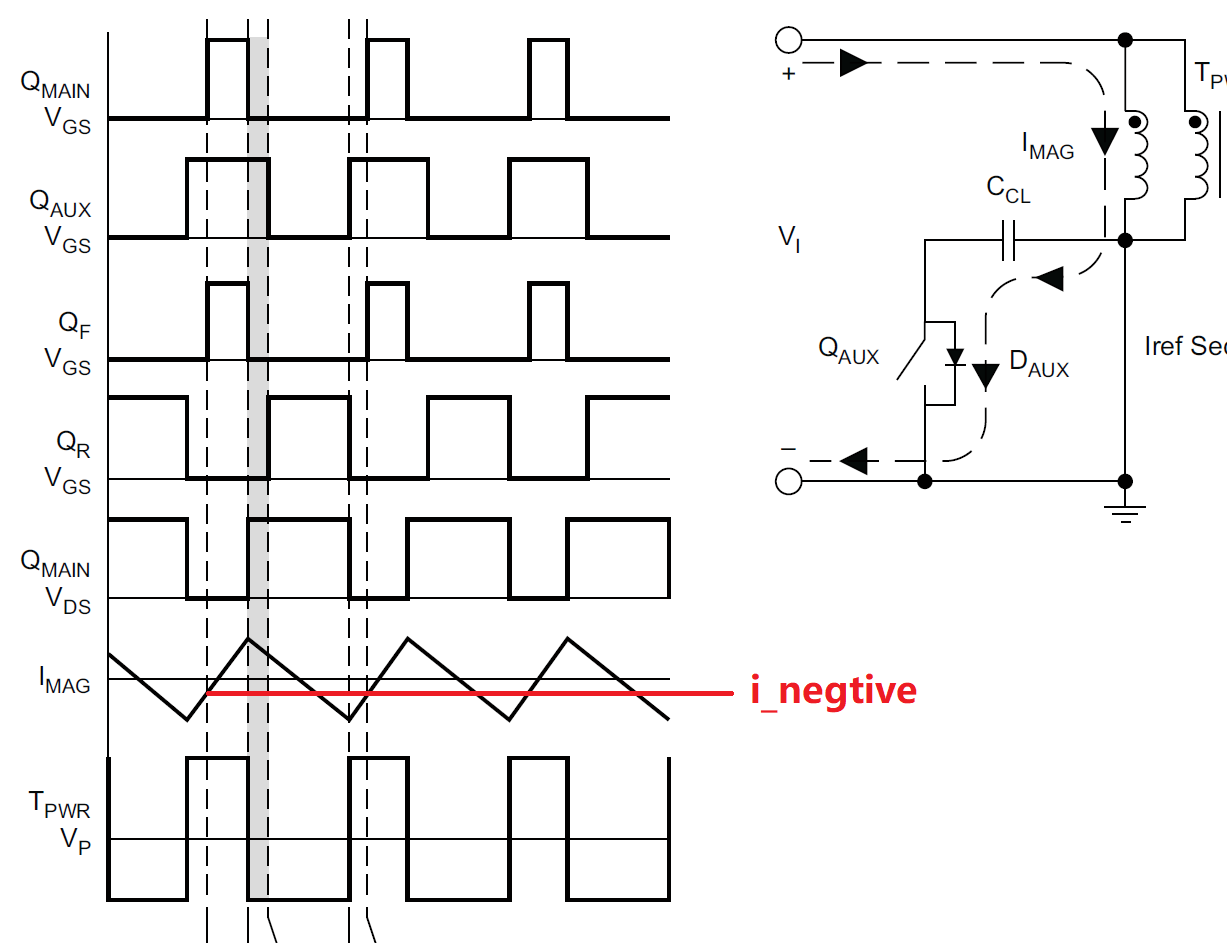

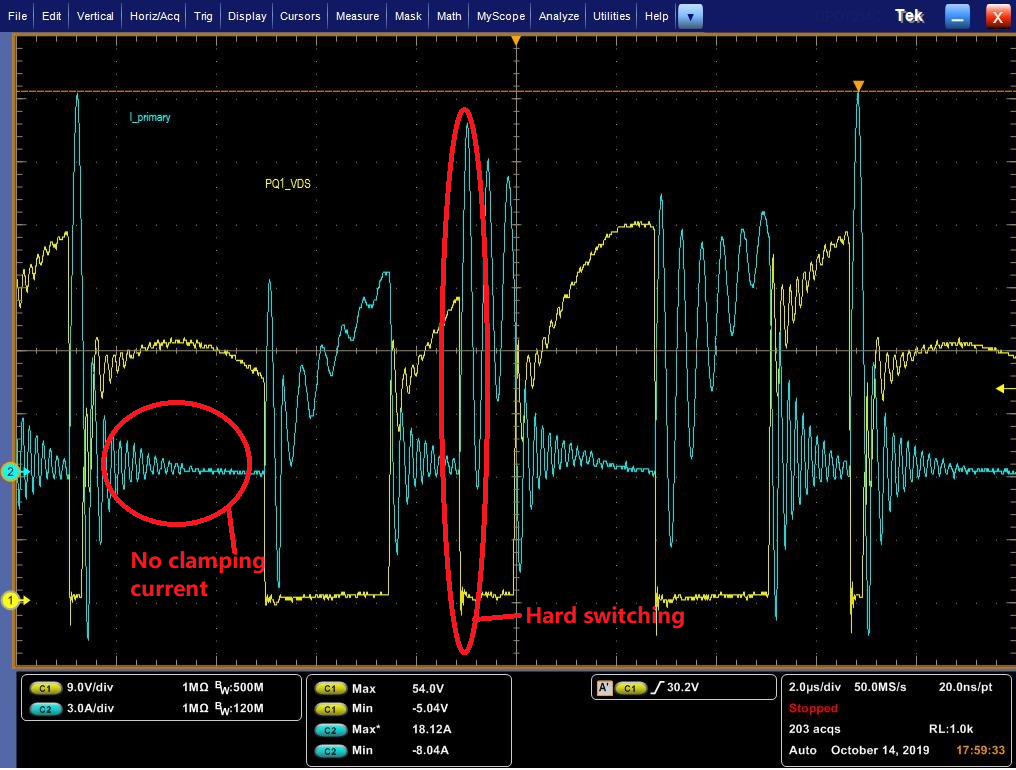

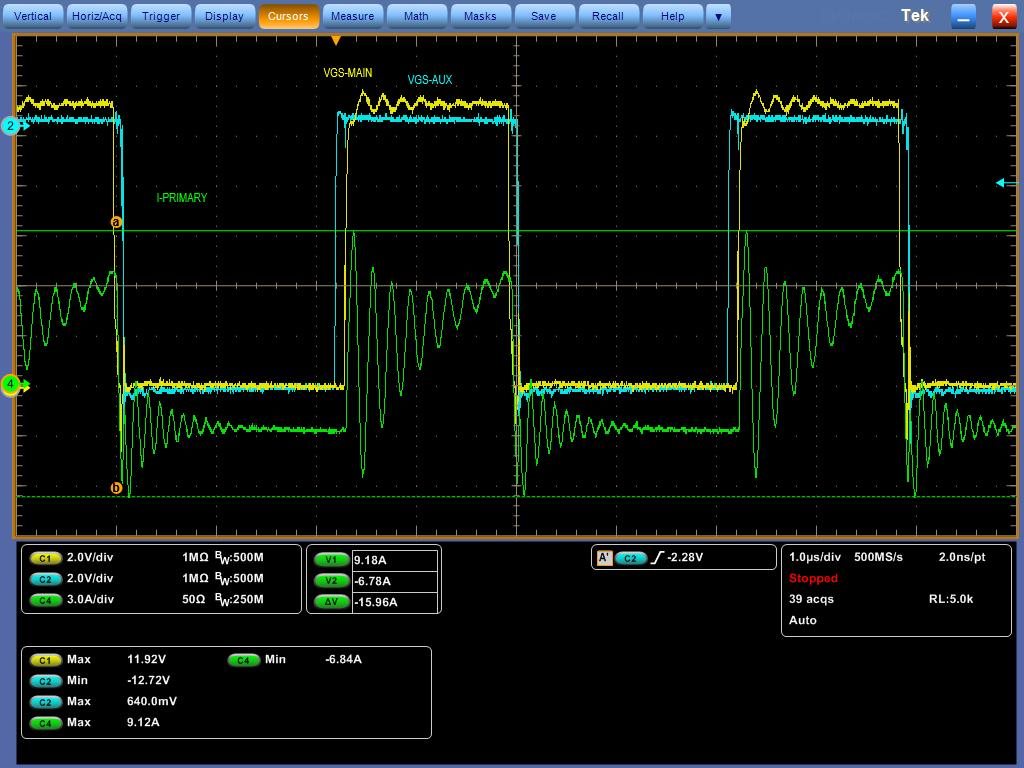

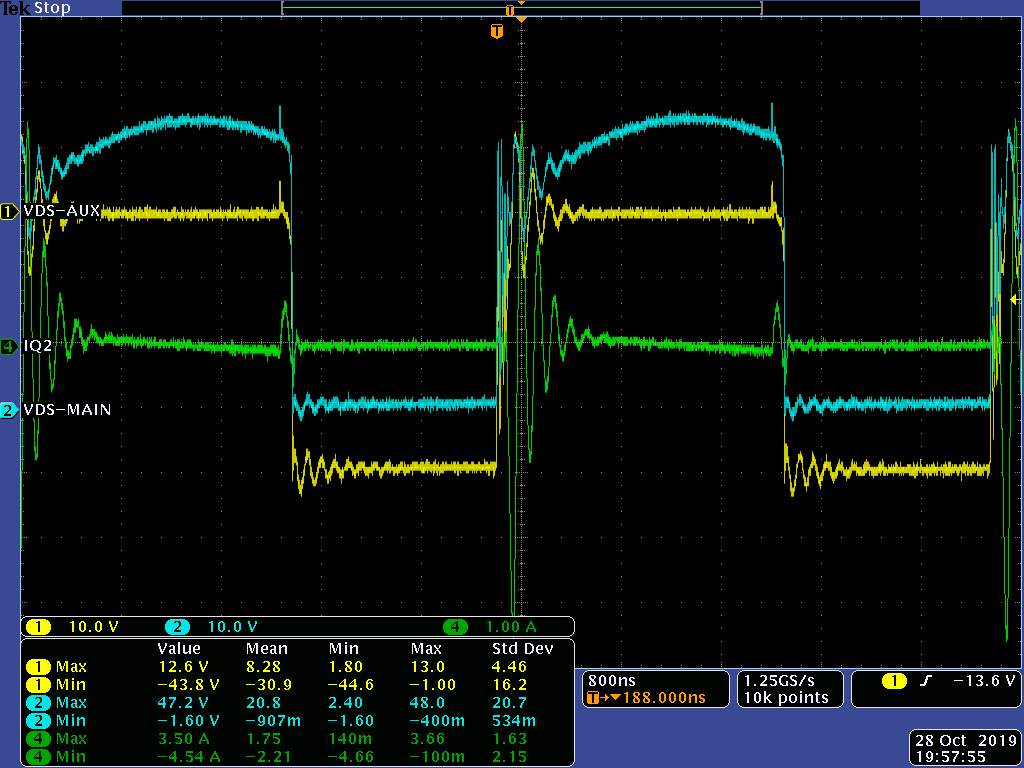

Our customer is using UCC2897A and we have the secondary side phase spike over spec and the spike is reach to 270V(CH2)@1,25A which is too high and over spec (the diode spec is only 200V). please see the waveform as below

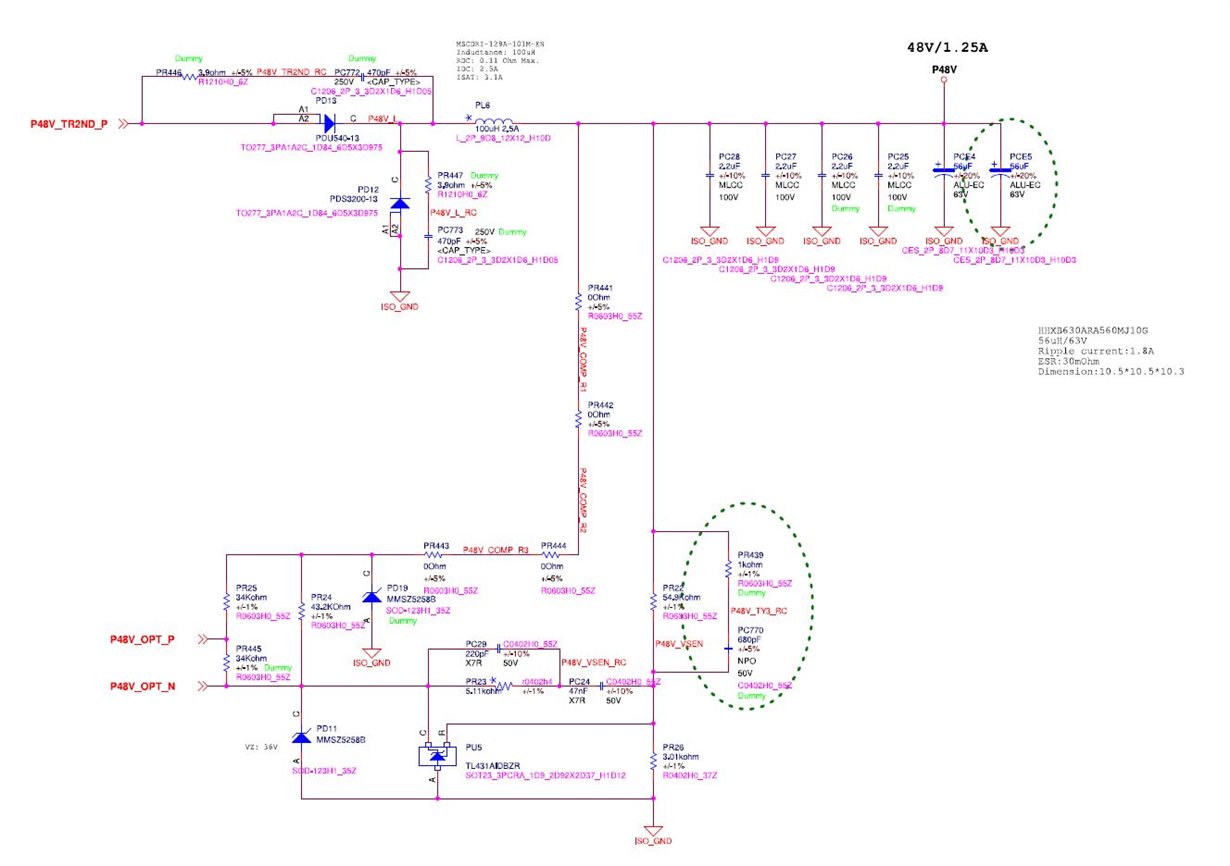

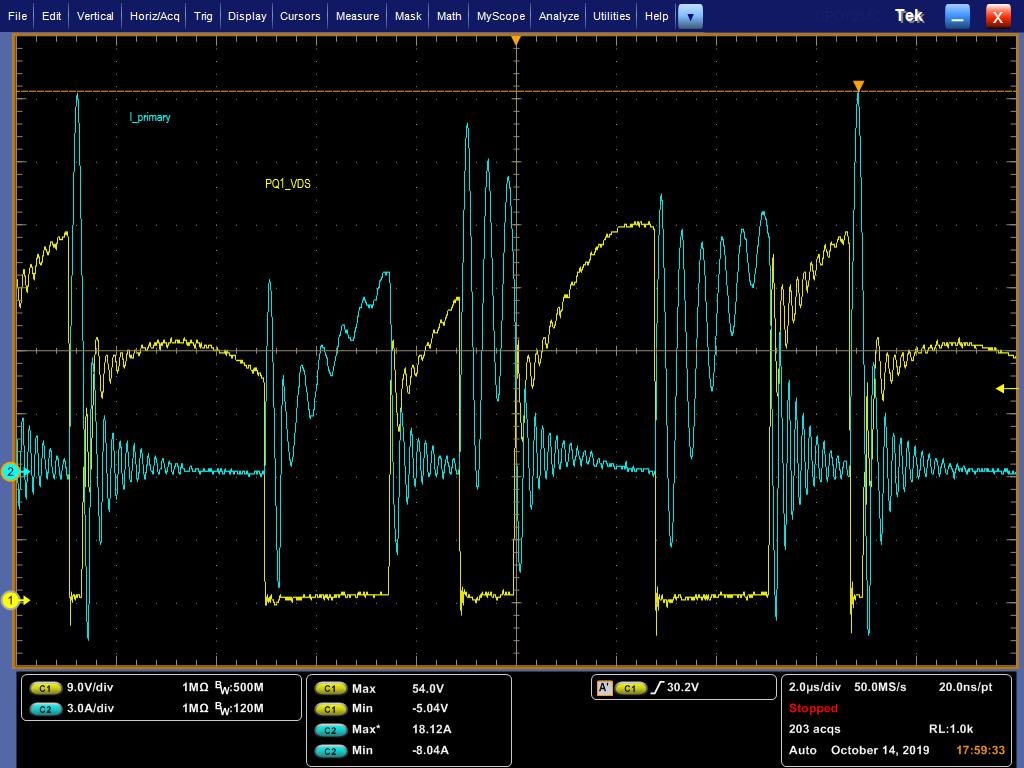

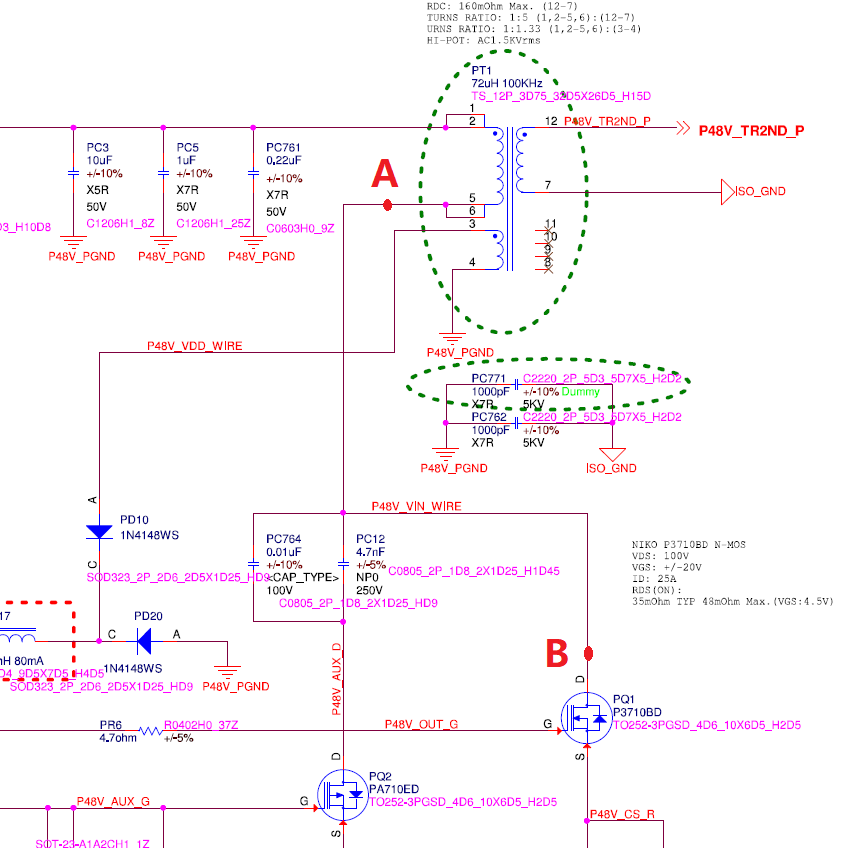

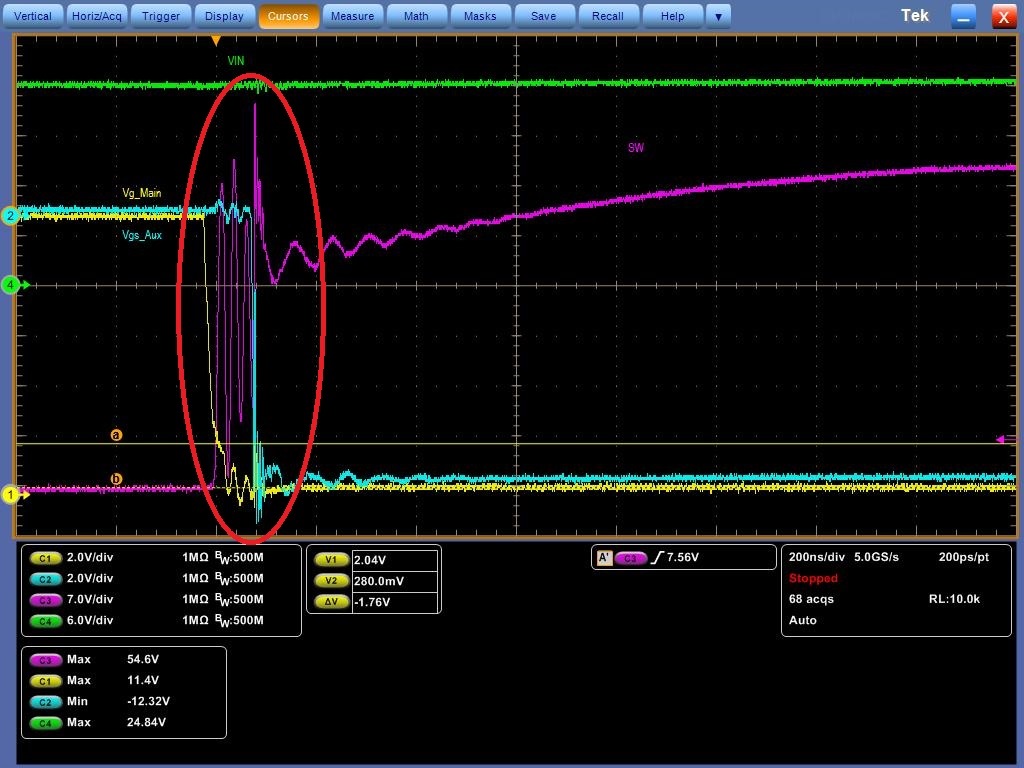

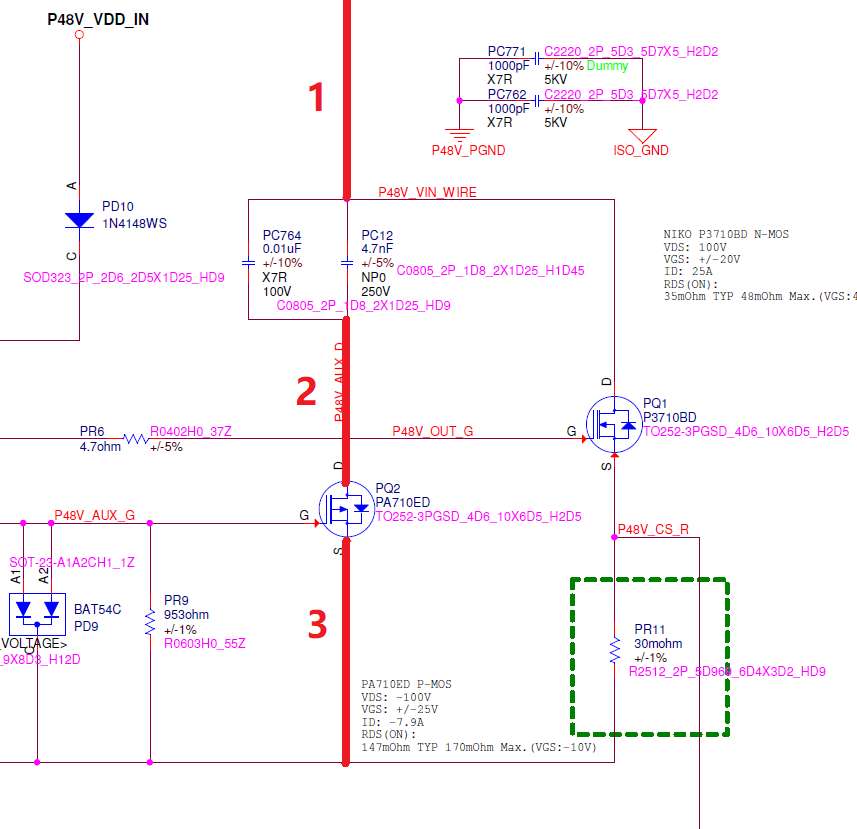

And we try to place snubber on PD12 and PD13. the snubbuer on PD13 have no improve on the spike and the one in the PD12 would improve the spike but it would have a spike pulse shown in the waveform below and also the waveform which RD can't use the solution. Could you kindly give us some suggestions to improve the spike(RD need to push the spike under 180V). we also attach the schematic as below

Above,please kindly help us with issue that we have and hope to hear for you soon

Cheers

Alec