Hi,

I received a question about startup behavior from a customer.

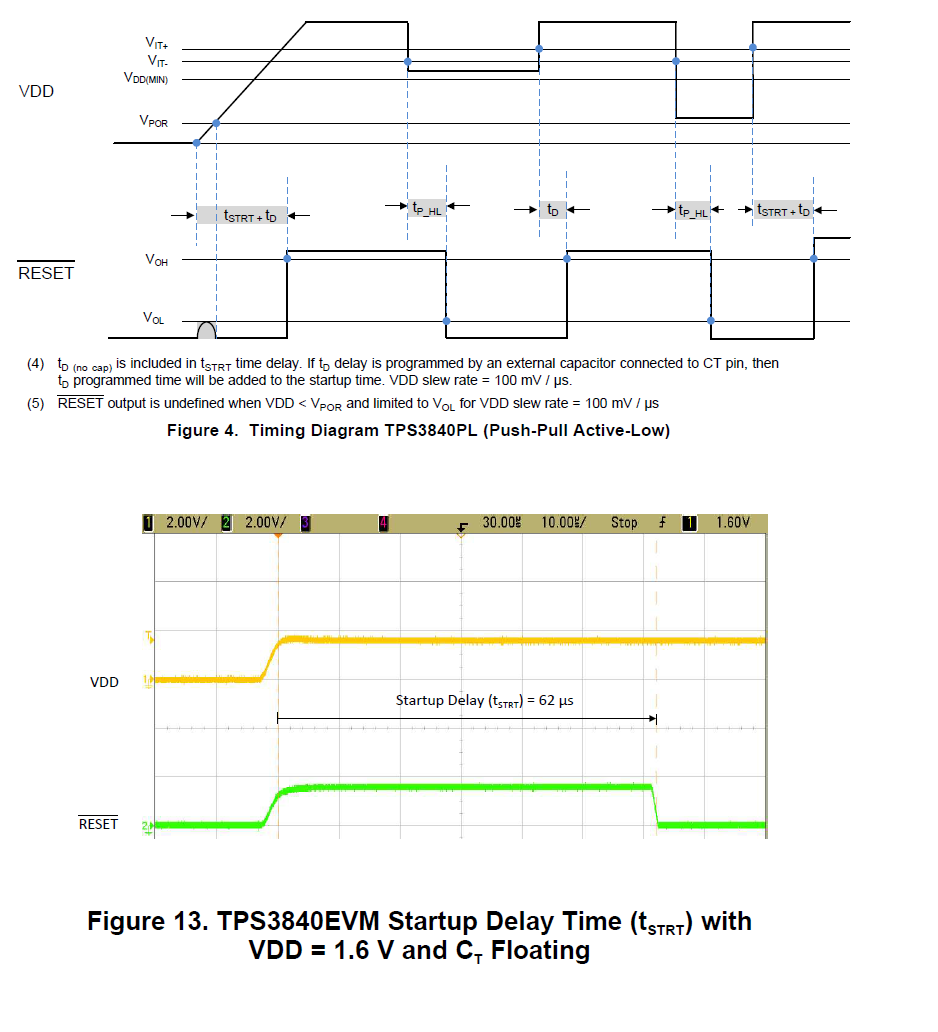

The figure above is an excerpt from the data sheet. (TPS3840PL)

The figure below is an EVM excerpt. (TPS3840DL)

My customer's question is whether RESET goes Hi when VDD does not reach VIT + at startup.

At startup, the EVM waveform is RESET high for 62us when VDD is between 1.6V and VIT +.

This indicates that it takes some time for RESET to take effect at startup.

Does the same behavior occur when VDD is between VPOR and 1.6V or less?